- 您现在的位置:买卖IC网 > PDF目录17100 > AD9146-M5375-EBZ (Analog Devices Inc)BOARD EVAL FOR AD9146 DAC PDF资料下载

参数资料

| 型号: | AD9146-M5375-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/56页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9146 DAC |

| 设计资源: | AD9146-M5375-EBZ Schematic AD9146-M5375-EBZ Gerber Files |

| 标准包装: | 1 |

| 系列: | TxDAC+® |

| DAC 的数量: | 2 |

| 位数: | 16 |

| 采样率(每秒): | 1G |

| 数据接口: | 串行 |

| 设置时间: | 20ns |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9146 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9146

Data Sheet

Rev. A | Page 20 of 56

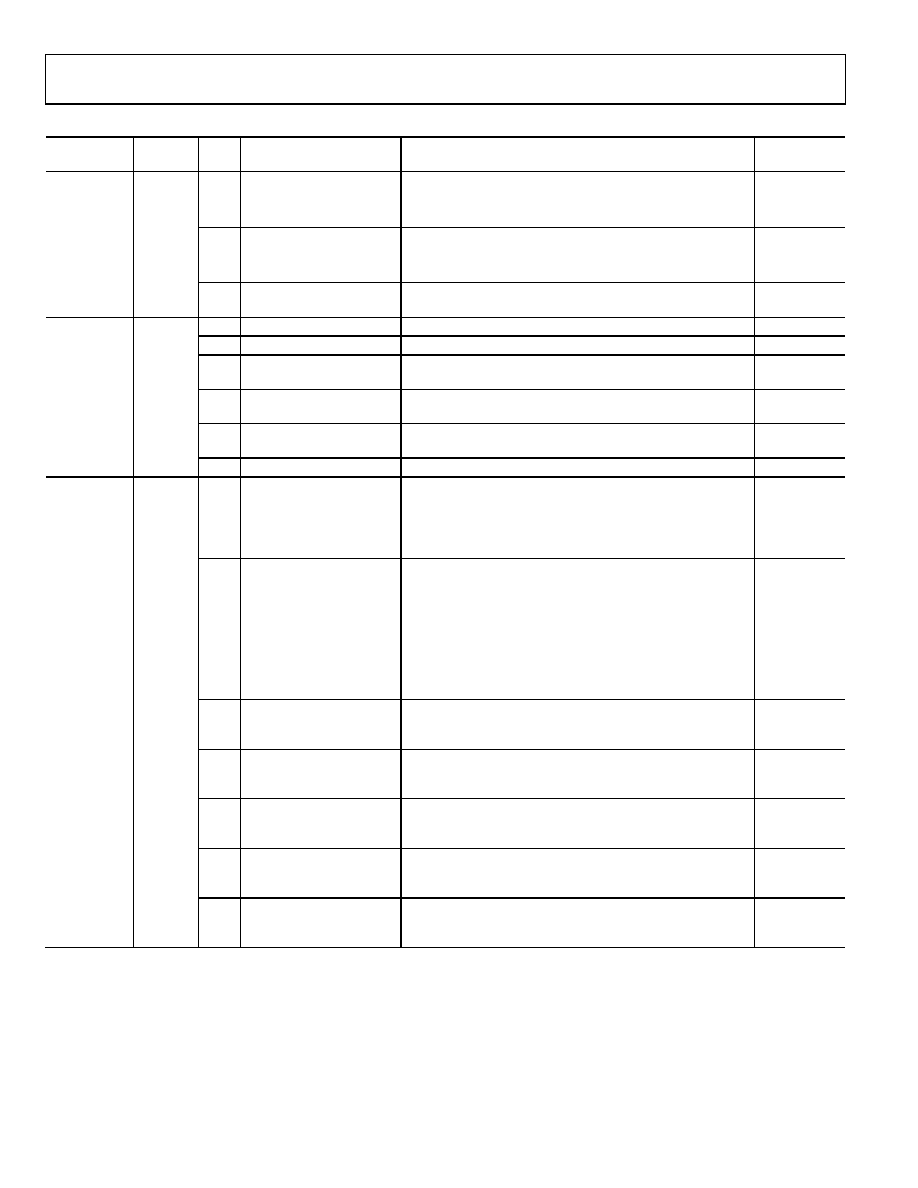

Table 11. Device Configuration Register Descriptions

Register

Name

Address

(Hex)

Bits

Name

Description

Default

Comm

0x00

7

SDIO

SDIO pin operation. To enable data readback, set this bit to 1.

0

0 = SDIO operates as an input only.

1 = SDIO operates as a bidirectional input/output.

6

LSB_FIRST

Serial port communication, LSB or MSB first.

0

0 = MSB first.

1 = LSB first.

5

Reset

The device is placed in reset when this bit is written high

and remains in reset until the bit is written low.

0

Power

Control

0x01

7

Power down I DAC

1 = power down I DAC.

0

6

Power down Q DAC

1 = power down Q DAC.

0

5

Power down data

receiver

1 = power down the input data receiver.

0

4

Power down auxiliary

ADC

1 = power down the auxiliary ADC for temperature sensor.

1

3

Power down auxiliary

DACs and reference

1 = power down the auxiliary DACs and the voltage reference.

0

2

Power down clocks

1 = power down the clocks.

0

Tx Enable

Control

0x02

6

Extended delay length

Time delay from when the TXENABLE pin is brought high to

when the DAC begins transmitting data. See the Tx Enable

section for more information.

0 = delay the outputs by 12 to 13 DAC/64 clock edges.

1 = delay the outputs by 19 to 20 DAC/64 clock edges.

0

5

Enable extended delay

The transmit delay, regardless of whether the extended delay

option is selected, has an inherent fixed delay of 10 DAC clock

cycles. When the extended delay is disabled, there is a mini-

mum delay time in the outputs of 1 to 2 DAC/64 clock edges

from when the TXENABLE pin is brought high.

0 = disable the extended delay option. Delays the outputs

by 1 to 2 DAC/64 clock edges.

1 = enable the extended delay option. Delays the outputs

based on the setting of Bit 6.

0

4

Power down voltage

reference

0 = no power-down of the internal voltage reference.

1 = power down the internal voltage reference when the

TXENABLE pin is held low.

0

3

Power down PLL

0 = no power-down of the on-chip PLL.

1 = power down the on-chip PLL when the TXENABLE pin is

held low.

0

2

Power down DACs

0 = no power-down of the DAC cores.

1 = power down the DAC cores when the TXENABLE pin is

held low.

0

1

Power down FIFO

0 = no power-down of the FIFO.

1 = power down the FIFO when the TXENABLE pin is held

low.

0

Power down filters

0 = no power-down of the interpolation filters.

1 = power down the interpolation filters when the

TXENABLE pin is held low.

0

相关PDF资料 |

PDF描述 |

|---|---|

| MCP355XDM-TAS | BOARD DEMO TINY APP SNSR MCP355X |

| LGU2D271MELY | CAP ALUM 270UF 200V 20% SNAP |

| MCP3551DM-PCTL | BOARD DEMO FOR MCP3551 |

| 0210490181 | CABLE JUMPER 1.25MM .203M 12POS |

| HL02150GTTR | INDUCTOR 15NH 200MA 0402 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9148 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad 16-Bit,1 GSPS, TxDAC+ Digital-to-Analog Converter |

| AD9148ARUZ | 制造商:Analog Devices 功能描述:- Rail/Tube |

| AD9148BBCZ | 功能描述:IC DAC 16BIT QD 1GSPS 196CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC+® 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD9148BBCZRL | 功能描述:IC DAC 16BIT QD 1GSPS 196CSPBGA RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC+® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD9148BBPZ | 功能描述:IC DAC 16BIT SPI/SRL 196BGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC+® 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

发布紧急采购,3分钟左右您将得到回复。