- 您现在的位置:买卖IC网 > PDF目录17059 > AD9148-M5375-EBZ (Analog Devices Inc)BOARD EVAL FOR AD9149, ADL5375 PDF资料下载

参数资料

| 型号: | AD9148-M5375-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/72页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9149, ADL5375 |

| 设计资源: | AD9148-M5375-EBZ Schematic AD9148-M5375-EBZ BOM AD9148-M5375-EBZ Gerber Files |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

AD9148

Data Sheet

Rev. B | Page 22 of 72

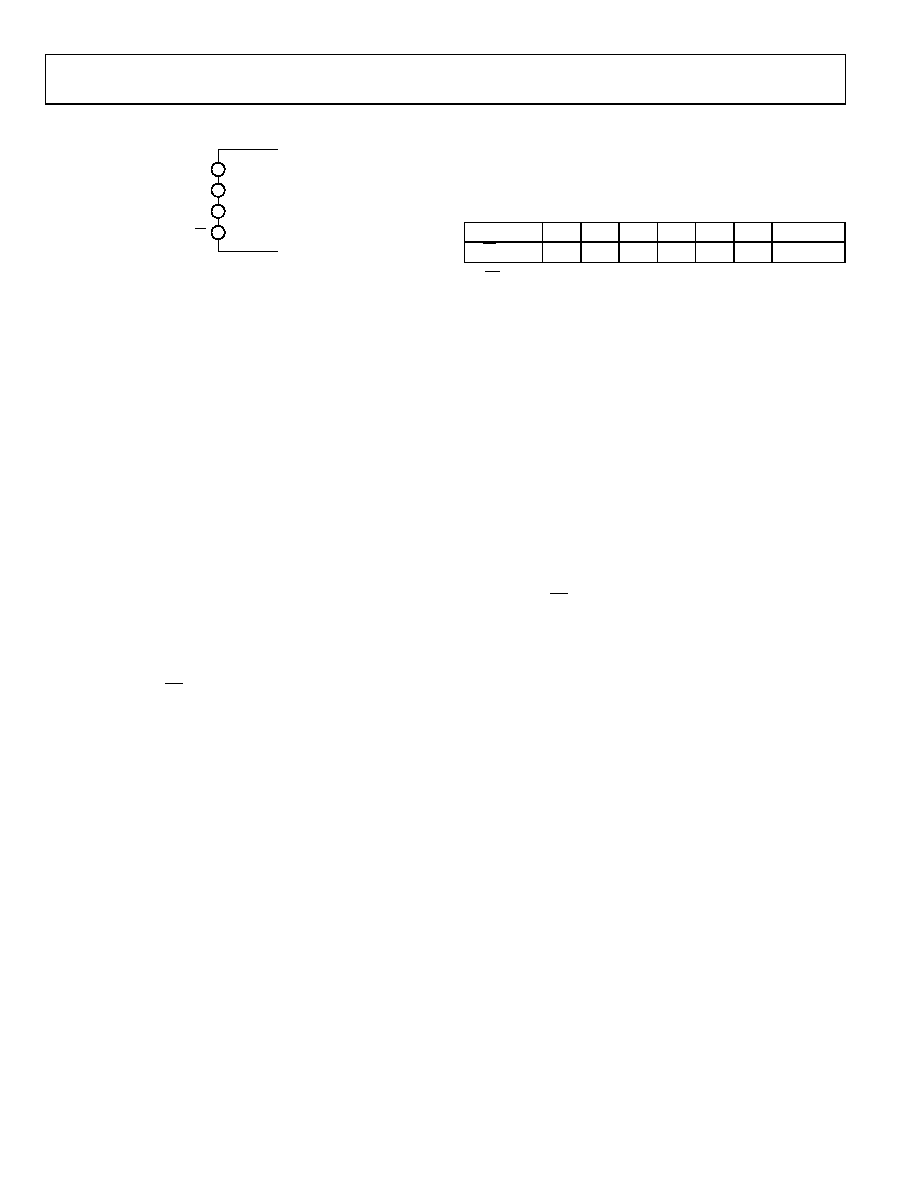

SERIAL PERIPHERAL INTERFACE

SDO

SPI

PORT

SDIO

SCLK

CS

G1

H1

G2

H2

08910-

040

Figure 40. SPI Por

t

The serial port is a flexible, synchronous serial communications

port allowing easy interface to many industry-standard micro-

controllers and microprocessors. The serial I/O is compatible

with most synchronous transfer formats, including both the

Motorola SPI and Intel SSR protocols. The interface allows

read/write access to all registers that configure the AD9148.

Single- or multiple-byte transfers are supported, as well as MSB-

first or LSB-first transfer formats. The serial interface ports can

be configured as a single pin I/O (SDIO) or two unidirectional

pins for input/output (SDIO/SDO).

GENERAL OPERATION OF THE SERIAL INTERFACE

There are two phases to a communication cycle with the AD9148.

Phase 1 is the instruction cycle (the writing of an instruction

byte into the device), coincident with the first eight SCLK rising

edges. The instruction byte provides the serial port controller

with information regarding the data transfer cycle, Phase 2 of

the communication cycle. The Phase 1 instruction byte defines

whether the upcoming data transfer is a read or a write, and the

starting register address for the first byte of the data transfer.

The first eight SCLK rising edges of each communication cycle

are used to write the instruction byte into the device.

A logic high on the CS pin followed by a logic low resets the SPI

port timing to the initial state of the instruction cycle. From this

state, the next eight rising SCLK edges represent the instruction

bits of the current I/O operation, regardless of the state of the

internal registers or the other signal levels at the inputs to the

SPI port. If the SPI port is in an instruction cycle or a data

transfer cycle, none of the present data is written.

The remaining SCLK edges are for Phase 2 of the communication

cycle. Phase 2 is the actual data transfer between the device and

the system controller. Phase 2 of the communication cycle is a

transfer of one or more data bytes. Registers change immediately

upon writing to the last bit of each transfer byte.

DATA FORMAT

The instruction byte contains the information shown in Table 11.

Table 11. SPI Instruction Byte

I7 (MSB)

I6

I5

I4

I3

I2

I1

I0 (LSB)

R/W

A6

A5

A4

A3

A2

A1

A0

R/W, Bit 7 of the instruction byte, determines whether a read or

a write data transfer occurs after the instruction byte write.

Logic high indicates a read operation, and Logic 0 indicates a

write operation.

A6 through A0, Bit 6 through Bit 0 of the instruction byte,

determine the register that is accessed during the data transfer

portion of the communication cycle. For multibyte transfers, this

address is the starting byte address. The remaining register

addresses are generated by the device based on the LSB-first bit

(Register 0x00, Bit 6).

SPI PIN DESCRIPTIONS

Serial Clock (SCLK)

The serial clock pin synchronizes data to and from the device

and runs the internal state machines. The maximum frequency

of SCLK is 40 MHz. All data input is registered on the rising

edge of SCLK. All data is driven out on the falling edge of SCLK.

Chip Select (CS)

Active low input starts and gates a communication cycle. It

allows more than one device to be used on the same serial

communications lines. The SDO and SDIO pins go to a high

impedance state when this input is high. Chip select should stay

low during the entire communication cycle.

Serial Data I/O (SDIO)

Data is always written into the device on this pin. However, this

pin can be used as a bidirectional data line. The configuration

of this pin is controlled by Register 0x00, Bit 7. The default is

Logic 0, configuring the SDIO pin as unidirectional.

Serial Data Output (SDO)

Data is read from this pin for protocols that use separate lines

for transmitting and receiving data. In the case where the device

operates in a single bidirectional I/O mode, this pin does not

output data and is set to a high impedance state.

相关PDF资料 |

PDF描述 |

|---|---|

| UPB2G181MRD6 | CAP ALUM 180UF 400V 20% RADIAL |

| VE-B64-EY | CONVERTER MOD DC/DC 48V 50W |

| AD9148-M5372-EBZ | BOARD EVAL FOR AD9149, ADL5372 |

| AD9737A-EBZ | BOARD EVAL FOR AD9737A |

| MIC2026-1YM | IC DISTRIBUTION SW DUAL 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9152BCPZ | 功能描述:16 Bit Digital to Analog Converter 2 56-LFCSP-WQ (8x8) 制造商:analog devices inc. 系列:TxDAC+? 包装:托盘 零件状态:有效 位数:16 数模转换器数:2 建立时间:- 输出类型:Current - Unbuffered 差分输出:是 数据接口:JESD204B 参考类型:内部 电压 - 电源,模拟:3.13 V ~ 3.47 V 电压 - 电源,数字:1.14 V ~ 1.26 V INL/DNL(LSB):±10,±5 架构:电流源 工作温度:-40°C ~ 85°C 封装/外壳:56-WFQFN 裸焊盘,CSP 供应商器件封装:56-LFCSP-WQ(8x8) 标准包装:1 |

| AD9152BCPZRL | 功能描述:16 Bit Digital to Analog Converter 2 56-LFCSP-WQ (8x8) 制造商:analog devices inc. 系列:TxDAC+? 包装:带卷(TR) 零件状态:有效 位数:16 数模转换器数:2 建立时间:- 输出类型:Current - Unbuffered 差分输出:是 数据接口:JESD204B 参考类型:内部 电压 - 电源,模拟:3.13 V ~ 3.47 V 电压 - 电源,数字:1.14 V ~ 1.26 V INL/DNL(LSB):±10,±5 架构:电流源 工作温度:-40°C ~ 85°C 封装/外壳:56-WFQFN 裸焊盘,CSP 供应商器件封装:56-LFCSP-WQ(8x8) 标准包装:2,500 |

| AD9152-EBZ | 功能描述:AD9152 TxDAC+? Series 16 Bit 2.25G Samples Per Second Digital to Analog Converter (DAC) Evaluation Board 制造商:analog devices inc. 系列:TxDAC+? 零件状态:有效 DAC 数:2 位数:16 采样率(每秒):2.25G 数据接口:SPI 建立时间:- DAC 类型:电流 工作温度:-40°C ~ 85°C 所含物品:板,线缆 使用的 IC/零件:AD9152 标准包装:1 |

| AD9152-FMC-EBZ | 功能描述:AD9152 TxDAC+? Series 16 Bit 2.25G Samples Per Second Digital to Analog Converter (DAC) Evaluation Board 制造商:analog devices inc. 系列:TxDAC+? 零件状态:有效 DAC 数:2 位数:16 采样率(每秒):2.25G 数据接口:SPI 建立时间:- DAC 类型:电流 工作温度:-40°C ~ 85°C 所含物品:板,线缆 使用的 IC/零件:AD9152 标准包装:1 |

| AD9152-M6720-EBZ | 功能描述:AD9152 TxDAC+? Series 16 Bit 2.25G Samples Per Second Digital to Analog Converter (DAC) Evaluation Board 制造商:analog devices inc. 系列:TxDAC+? 零件状态:有效 DAC 数:2 位数:16 采样率(每秒):2.25G 数据接口:SPI 建立时间:- DAC 类型:电流 工作温度:-40°C ~ 85°C 所含物品:板 使用的 IC/零件:AD9152 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。