- 您现在的位置:买卖IC网 > PDF目录17059 > AD9148-M5375-EBZ (Analog Devices Inc)BOARD EVAL FOR AD9149, ADL5375 PDF资料下载

参数资料

| 型号: | AD9148-M5375-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 44/72页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9149, ADL5375 |

| 设计资源: | AD9148-M5375-EBZ Schematic AD9148-M5375-EBZ BOM AD9148-M5375-EBZ Gerber Files |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

Data Sheet

AD9148

Rev. B | Page 49 of 72

INTERFACE TIMING

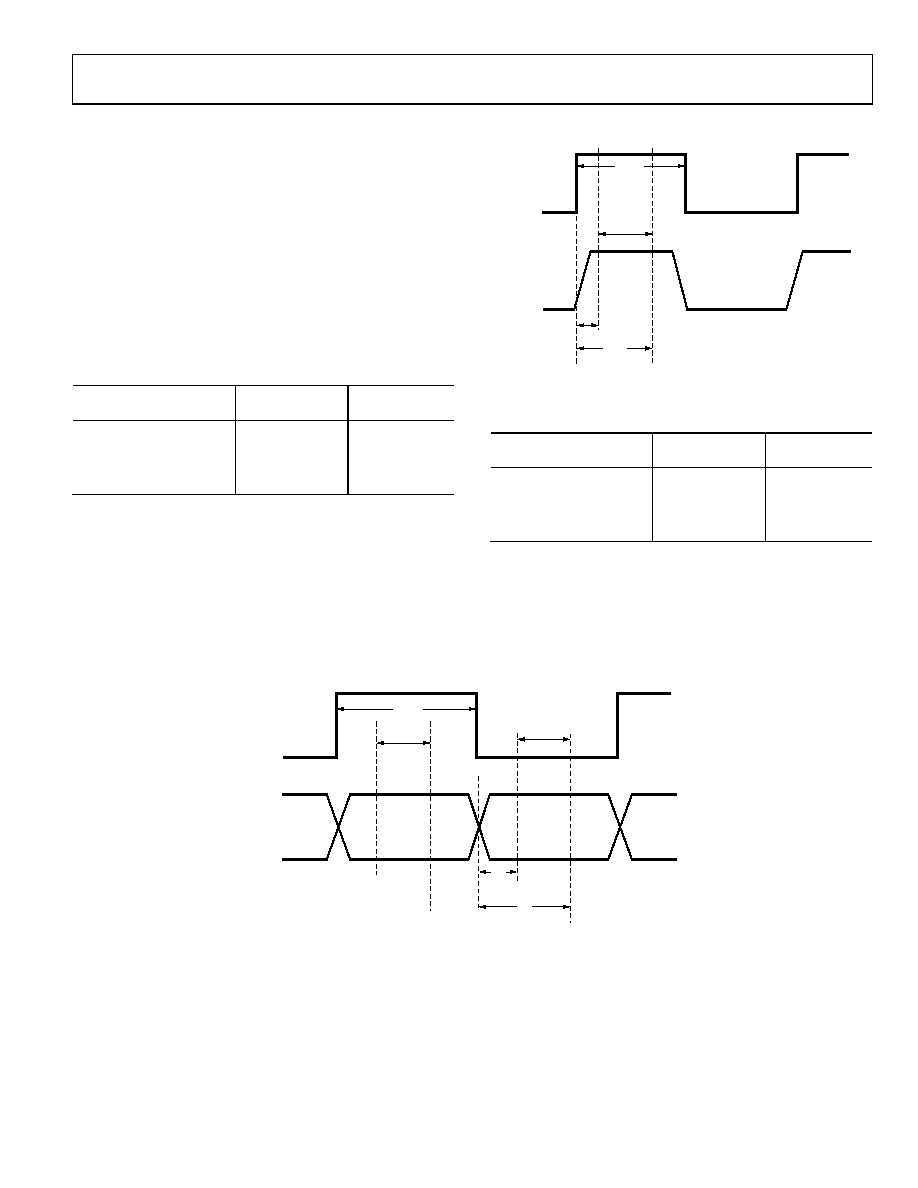

The timing diagram for the digital interface port is shown in

Figure 59. The sampling point of the data bus nominally occurs

250 ps after each edge of the DCI signal and has an uncertainty of

± 250 ps when the DCI delay is set to 00b (Register 0x72[1:0]),

as illustrated by the sampling interval. The data and FRAME

signals must be valid throughout this sampling interval. The data

and FRAME signals may change at any time between sampling

intervals.

The setup (tS) and hold (tH) times with respect to the edges are

shown in Figure 59. The minimum setup and hold times are

shown in Table 16.

Table 16. Data Port Setup and Hold Times

DCI Delay

(Register 0x72, Bits[1:0])

Minimum Setup

Time, tS (ns)

Minimum Hold

Time, tH (ns)

00

0.02

0.52

01

0.16

0.78

10

0.28

1.03

11

0.36

1.16

The data interface timing can be verified by using the SED

circuitry. See the Interface Timing Validation section for details.

In data rate mode with synchronization enabled, a second timing

constraint between DCI and DACCLK must be met in addition

to the DCI-to-data timing shown in Table 17. In data rate mode,

only one FIFO slot is being used. The DCI to DACCLK timing

restriction is required to prevent data being written to and read

from the FIFO slot at the same time. The required timing

between DCI and DACCLK is shown in Figure 58.

DCI

DACCLK/

REFCLK

tDATA

tSDCI

tHDCI

SAMPLING

INTERVAL

08

91

0-

057

Figure 58. Timing Diagram for Input Data Port (Data Rate Mode with Sync On)

Table 17. DCI to DACCLK Setup and Hold Times vs. DCI

Delay Value

DCI Delay

(Register 0x72,Bits[1:0])

Minimum Setup

Time, tSDCI (ns)

Minimum Hold

Time, tHDCI (ns)

00

0.06

0.85

01

0.22

1.14

10

0.36

1.43

11

0.45

1.59

tDATA

tS

tH

SAMPLING

INTERVAL

DCI

DATA

SAMPLING

INTERVAL

08

91

0-

05

8

Figure 59. Timing Diagram for Input Data Ports

相关PDF资料 |

PDF描述 |

|---|---|

| UPB2G181MRD6 | CAP ALUM 180UF 400V 20% RADIAL |

| VE-B64-EY | CONVERTER MOD DC/DC 48V 50W |

| AD9148-M5372-EBZ | BOARD EVAL FOR AD9149, ADL5372 |

| AD9737A-EBZ | BOARD EVAL FOR AD9737A |

| MIC2026-1YM | IC DISTRIBUTION SW DUAL 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9152BCPZ | 功能描述:16 Bit Digital to Analog Converter 2 56-LFCSP-WQ (8x8) 制造商:analog devices inc. 系列:TxDAC+? 包装:托盘 零件状态:有效 位数:16 数模转换器数:2 建立时间:- 输出类型:Current - Unbuffered 差分输出:是 数据接口:JESD204B 参考类型:内部 电压 - 电源,模拟:3.13 V ~ 3.47 V 电压 - 电源,数字:1.14 V ~ 1.26 V INL/DNL(LSB):±10,±5 架构:电流源 工作温度:-40°C ~ 85°C 封装/外壳:56-WFQFN 裸焊盘,CSP 供应商器件封装:56-LFCSP-WQ(8x8) 标准包装:1 |

| AD9152BCPZRL | 功能描述:16 Bit Digital to Analog Converter 2 56-LFCSP-WQ (8x8) 制造商:analog devices inc. 系列:TxDAC+? 包装:带卷(TR) 零件状态:有效 位数:16 数模转换器数:2 建立时间:- 输出类型:Current - Unbuffered 差分输出:是 数据接口:JESD204B 参考类型:内部 电压 - 电源,模拟:3.13 V ~ 3.47 V 电压 - 电源,数字:1.14 V ~ 1.26 V INL/DNL(LSB):±10,±5 架构:电流源 工作温度:-40°C ~ 85°C 封装/外壳:56-WFQFN 裸焊盘,CSP 供应商器件封装:56-LFCSP-WQ(8x8) 标准包装:2,500 |

| AD9152-EBZ | 功能描述:AD9152 TxDAC+? Series 16 Bit 2.25G Samples Per Second Digital to Analog Converter (DAC) Evaluation Board 制造商:analog devices inc. 系列:TxDAC+? 零件状态:有效 DAC 数:2 位数:16 采样率(每秒):2.25G 数据接口:SPI 建立时间:- DAC 类型:电流 工作温度:-40°C ~ 85°C 所含物品:板,线缆 使用的 IC/零件:AD9152 标准包装:1 |

| AD9152-FMC-EBZ | 功能描述:AD9152 TxDAC+? Series 16 Bit 2.25G Samples Per Second Digital to Analog Converter (DAC) Evaluation Board 制造商:analog devices inc. 系列:TxDAC+? 零件状态:有效 DAC 数:2 位数:16 采样率(每秒):2.25G 数据接口:SPI 建立时间:- DAC 类型:电流 工作温度:-40°C ~ 85°C 所含物品:板,线缆 使用的 IC/零件:AD9152 标准包装:1 |

| AD9152-M6720-EBZ | 功能描述:AD9152 TxDAC+? Series 16 Bit 2.25G Samples Per Second Digital to Analog Converter (DAC) Evaluation Board 制造商:analog devices inc. 系列:TxDAC+? 零件状态:有效 DAC 数:2 位数:16 采样率(每秒):2.25G 数据接口:SPI 建立时间:- DAC 类型:电流 工作温度:-40°C ~ 85°C 所含物品:板 使用的 IC/零件:AD9152 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。