- 您现在的位置:买卖IC网 > PDF目录1985 > AD9222ABCPZRL7-65 (Analog Devices Inc)IC ADC 12BIT SRL 65MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9222ABCPZRL7-65 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/60页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT SRL 65MSPS 64LFCSP |

| 标准包装: | 750 |

| 位数: | 12 |

| 采样率(每秒): | 65M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 8 |

| 功率耗散(最大): | 950.5mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 16 个单端,单极;8 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

AD9222

Data Sheet

Rev. F | Page 38 of 60

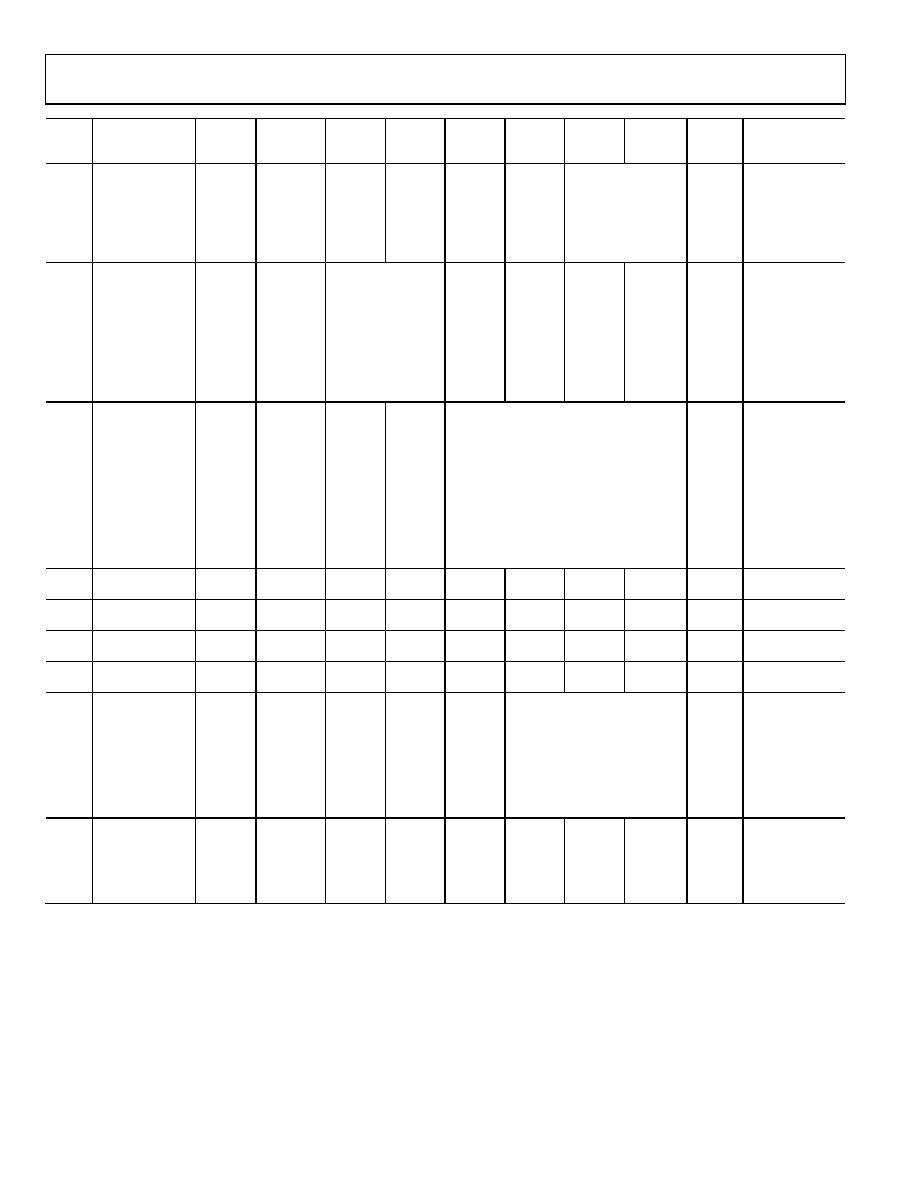

Addr.

(Hex)

Parameter Name

(MSB)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

(LSB)

Bit 0

Default

Value

(Hex)

Default Notes/

Comments

14

output_mode

X

0 = LVDS

ANSI-644

(default)

1 = LVDS

low power,

(IEEE1596.3

similar)

X

Output

invert

1 = on

0 = off

(default)

00 = offset binary

(default)

01 = twos

complement

0x00

Configures the

outputs and the

format of the data.

15

output_adjust

X

Output driver

termination

00 = none (default)

01 = 200

10 = 100

11 = 100

X

DCO and

FCO

2× Drive

Strength

1 = on

0 = off

(default)

0x00

Determines

LVDS or other

output properties.

Primarily func-

tions to set the

LVDS span and

common-mode

levels in place of

an external

resistor.

16

output_phase

X

0011 = output clock phase adjust

(0000 through 1010)

0000 = 0° relative to data edge

0001 = 60° relative to data edge

0010 = 120° relative to data edge

0011 = 180° relative to data edge (default)

0101 = 300° relative to data edge

0110 = 360° relative to data edge

1000 = 480° relative to data edge

1001 = 540° relative to data edge

1010 = 600° relative to data edge

1011 to 1111 = 660° relative to data edge

0x03

On devices that

utilize global

clock divide,

determines

which phase of

the divider

output is used to

supply the

output clock.

Internal latching

is unaffected.

19

user_patt1_lsb

B7

B6

B5

B4

B3

B2

B1

B0

0x00

User-defined

pattern, 1 LSB.

1A

user_patt1_msb

B15

B14

B13

B12

B11

B10

B9

B8

0x00

User-defined

pattern, 1 MSB.

1B

user_patt2_lsb

B7

B6

B5

B4

B3

B2

B1

B0

0x00

User-defined

pattern, 2 LSB.

1C

user_patt2_msb

B15

B14

B13

B12

B11

B10

B9

B8

0x00

User-defined

pattern, 2 MSB.

21

serial_control

LSB first

1 = on

0 = off

(default)

X

<10

MSPS,

low

encode

rate

mode

1 = on

0 = off

(default)

000 = 12 bits (default, normal bit

stream)

001 = 8 bits

010 = 10 bits

011 = 12 bits

100 = 14 bits

0x00

Serial stream

control. Default

causes MSB first

and the native

bit stream

(global).

22

serial_ch_stat

X

Channel

output

reset

1 = on

0 = off

(default)

Channel

power-

down

1 = on

0 = off

(default)

0x00

Used to power

down individual

sections of a

converter (local).

相关PDF资料 |

PDF描述 |

|---|---|

| AD9224ARSZRL | IC ADC 12BIT 40MSPS 28SSOP |

| AD9225ARS | IC ADC 12BIT 25MSPS 28-SSOP |

| AD9226ASTRL | IC ADC 12BIT 65MSPS 48-LQFP |

| AD9228ABCPZRL7-65 | IC ADC 12BIT SPI/SRL 65M 48LFCSP |

| AD9229ABCPZRL7-65 | IC ADC 12BIT SRL 65MSPS 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9222BCPZ-40 | 制造商:Analog Devices 功能描述:Octal ADC Pipelined 40Msps 12-bit Serial 64-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述: |

| AD9222BCPZ-50 | 制造商:Analog Devices 功能描述:ADC Octal Pipelined 50Msps 12-bit Serial 64-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:12BIT ADC OCTAL 50MSPS LFCSP-64 |

| AD9222BCPZ-65 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9222BCPZRL7-40 | 制造商:AD 制造商全称:Analog Devices 功能描述:Octal, 12-Bit, 40/50 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9222BCPZRL7-50 | 制造商:Analog Devices 功能描述:ADC Octal Pipelined 50Msps 12-bit Serial 64-Pin LFCSP EP T/R |

发布紧急采购,3分钟左右您将得到回复。