- 您现在的位置:买卖IC网 > PDF目录10051 > AD9257BCPZRL7-40 (Analog Devices Inc)IC ADC 14BIT SRL 40MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9257BCPZRL7-40 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/40页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT SRL 40MSPS 64LFCSP |

| 标准包装: | 750 |

| 位数: | 14 |

| 采样率(每秒): | 40M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 8 |

| 功率耗散(最大): | 434mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 8 个差分 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

Data Sheet

AD9257

Rev. A | Page 21 of 40

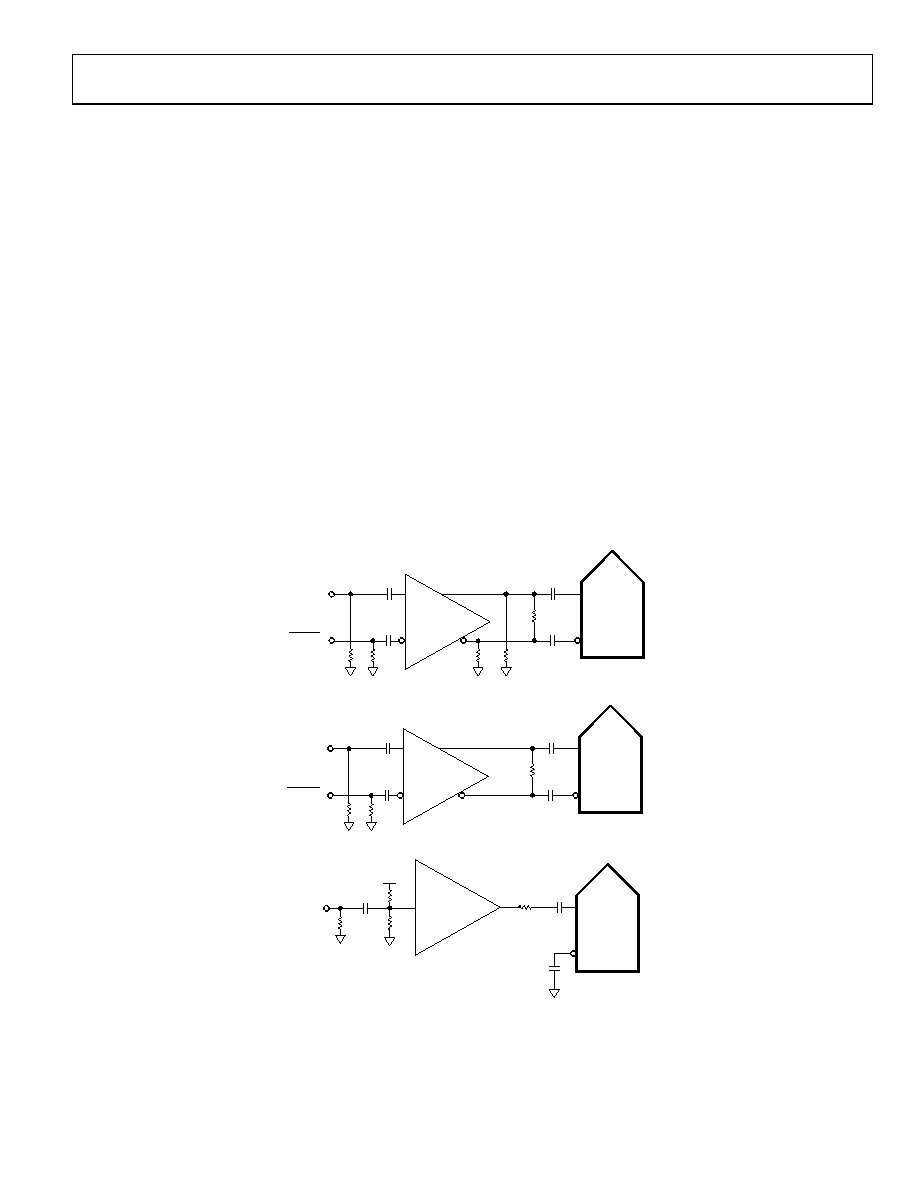

If a low jitter clock source is not available, another option is to

ac couple a differential PECL signal to the sample clock input

excellent jitter performance.

A third option is to ac couple a differential LVDS signal to the

sample clock input pins, as shown in Figure 53. The AD9510/

clock drivers offer excellent jitter performance.

In some applications, it may be acceptable to drive the sample

clock inputs with a single-ended 1.8 V CMOS signal. In such

applications, drive the CLK+ pin directly from a CMOS gate, and

bypass the CLK pin to ground with a 0.1 μF capacitor (see

Input Clock Divider

The AD9257 contains an input clock divider with the ability

to divide the input clock by integer values between 1 and 8.

The AD9257 clock divider can be synchronized using the

external SYNC input. Bit 0 and Bit 1 of Register 0x109 allow the

clock divider to be resynchronized on every SYNC signal or

only on the first SYNC signal after the register is written. A

valid SYNC causes the clock divider to reset to its initial state.

This synchronization feature allows multiple parts to have their

clock dividers aligned to guarantee simultaneous input sampling.

Clock Duty Cycle

Typical high speed ADCs use both clock edges to generate a vari-

ety of internal timing signals and, as a result, may be sensitive to

clock duty cycle. Commonly, a ±5% tolerance is required on the

clock duty cycle to maintain dynamic performance characteristics.

The AD9257 contains a duty cycle stabilizer (DCS) that retimes

the nonsampling (falling) edge, providing an internal clock signal

with a nominal 50% duty cycle. This allows the user to provide

a wide range of clock input duty cycles without affecting the per-

formance of the AD9257. Noise and distortion performance are

nearly flat for a wide range of duty cycles with the DCS on.

Jitter in the rising edge of the input is still of concern and is not

easily reduced by the internal stabilization circuit. The duty

cycle control loop does not function for clock rates less than

20 MHz, nominally. The loop has a time constant associated

with it that must be considered in applications in which the

clock rate can change dynamically. A wait time of 1.5 s to 5 s

is required after a dynamic clock frequency increase or decrease

before the DCS loop is relocked to the input signal.

10

0

0.1F

240

50k

CLK–

CLK+

CLOCK

INPUT

CLOCK

INPUT

ADC

AD951x

PECL DRIVER

10206-

051

Figure 52. Differential PECL Sample Clock (Up to 520 MHz)

10

0

0.1F

50k

CLK–

CLK+

ADC

CLOCK

INPUT

CLOCK

INPUT

AD951x

LVDS DRIVER

10206-

052

Figure 53. Differential LVDS Sample Clock (Up to 520 MHz)

OPTIONAL

100

0.1F

501

1

50 RESISTOR IS OPTIONAL.

CLK–

CLK+

ADC

VCC

1k

CLOCK

INPUT

AD951x

CMOS DRIVER

10206-

053

Figure 54. Single-Ended 1.8 V CMOS Input Clock (Up to 200 MHz)

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102A28-21PY | CONN RCPT 37POS BOX MNT W/PINS |

| D38999/20FB98PNPC | CONN RCPT 6POS WALL MNT W/PINS |

| MS3102A28-21PX | CONN RCPT 37POS BOX MNT W/PINS |

| AD7875KP | IC ADC 12BIT SAMPLING 5V 28PLCC |

| LTC489IN#PBF | IC LINE RCVR RS485 QUAD 16-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9257BCPZRL7-65 | 功能描述:IC ADC 14BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD9257TCPZ-65-EP | 功能描述:14 Bit Analog to Digital Converter 8 Input 8 Pipelined 64-LFCSP-WQ (9x9) 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 位数:14 采样率(每秒):65M 输入数:8 输入类型:差分 数据接口:LVDS - 串行 配置:S/H-ADC 无线电 - S/H:ADC:1:1 A/D 转换器数:8 架构:管线 参考类型:内部 电压 - 电源,模拟:1.7 V ~ 1.9 V 电压 - 电源,数字:1.7 V ~ 1.9 V 特性:同步采样 工作温度:-55°C ~ 125°C 封装/外壳:64-WFQFN 裸露焊盘 供应商器件封装:64-LFCSP-WQ(9x9) 标准包装:1 |

| AD9258 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9258-105EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9258-125EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

发布紧急采购,3分钟左右您将得到回复。