- 您现在的位置:买卖IC网 > PDF目录10051 > AD9257BCPZRL7-40 (Analog Devices Inc)IC ADC 14BIT SRL 40MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9257BCPZRL7-40 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/40页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT SRL 40MSPS 64LFCSP |

| 标准包装: | 750 |

| 位数: | 14 |

| 采样率(每秒): | 40M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 8 |

| 功率耗散(最大): | 434mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 8 个差分 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页

AD9257

Data Sheet

Rev. A | Page 6 of 40

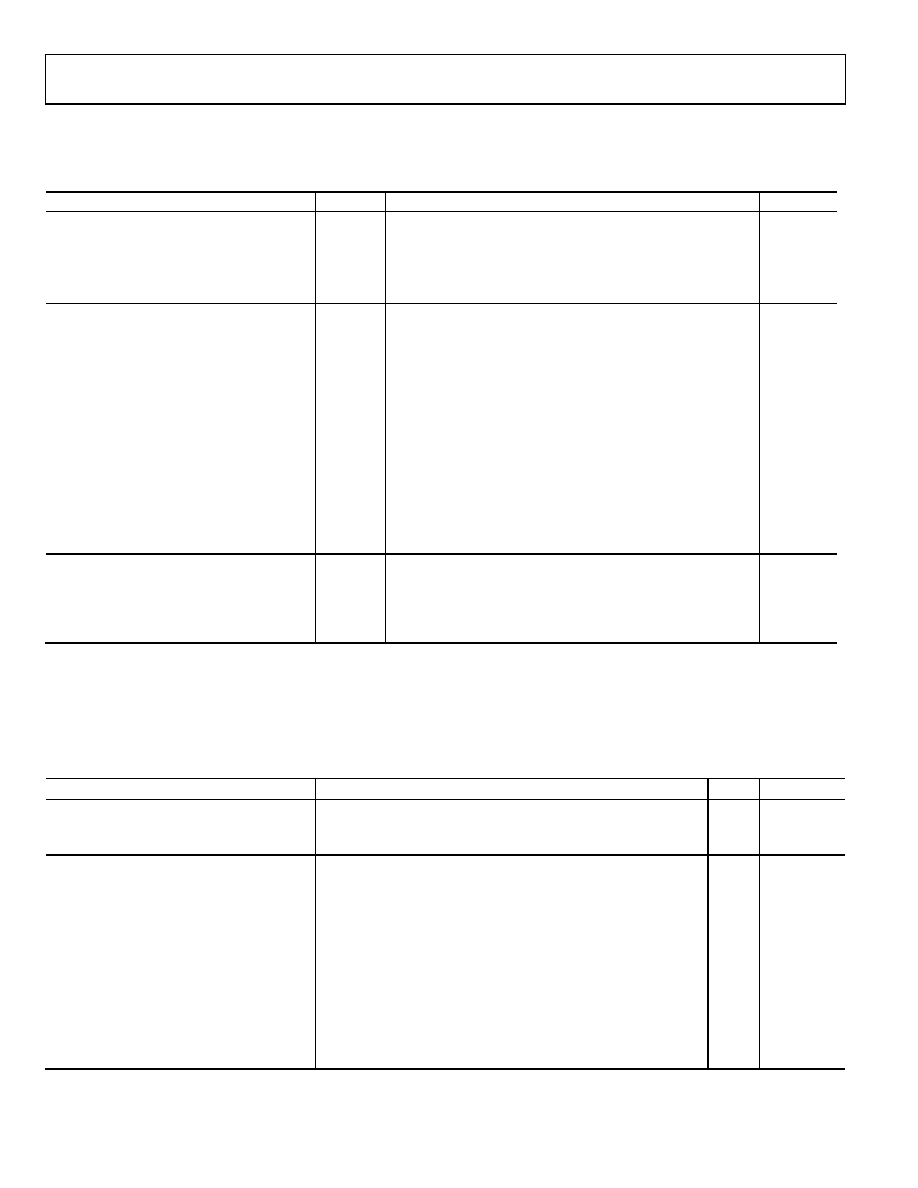

SWITCHING SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, 2 V p-p differential input, 1.0 V internal reference, AIN = 1.0 dBFS, unless otherwise noted.

Table 4.

Parameter1, 2

Temp

Min

Typ

Max

Unit

CLOCK3

Input Clock Rate

Full

10

520

MHz

Conversion Rate

Full

10

40/65

MSPS

Clock Pulse Width High (tEH)

Full

12.5/7.69

ns

Clock Pulse Width Low (tEL)

Full

12.5/7.69

ns

OUTPUT PARAMETERS3

Propagation Delay (tPD)

Full

1.5

2.3

3.1

ns

Rise Time (tR) (20% to 80%)

Full

300

ps

Fall Time (tF) (20% to 80%)

Full

300

ps

FCO Propagation Delay (tFCO)

Full

1.5

2.3

3.1

ns

DCO Propagation Delay (tCPD)4

Full

tFCO + (tSAMPLE/28)

ns

DCO to Data Delay (tDATA)4

Full

(tSAMPLE/28) 300

(tSAMPLE/28)

(tSAMPLE/28) + 300

ps

DCO to FCO Delay (tFRAME)4

Full

(tSAMPLE/28) 300

(tSAMPLE/28)

(tSAMPLE/28) + 300

ps

Data to Data Skew

(tDATA-MAX tDATA-MIN)

Full

±50

±200

ps

Wake-Up Time (Standby)

25°C

35

μs

Wake-Up Time (Power-Down)5

25°C

375

μs

Pipeline Latency

Full

16

Clock

cycles

APERTURE

Aperture Delay (tA)

25°C

1

ns

Aperture Uncertainty (Jitter)

25°C

0.1

ps rms

Out-of-Range Recovery Time

25°C

1

Clock

cycles

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for definitions and for details on how these tests were completed.

2

Measured on standard FR-4 material.

3

Can be adjusted via the SPI.

4

tSAMPLE/28 is based on the number of bits divided by 2 because the delays are based on half duty cycles. tSAMPLE = 1/fS.

5

Wake-up time is defined as the time required to return to normal operation from power-down mode.

TIMING SPECIFICATIONS

Table 5.

Parameter

Description

Limit

Unit

SYNC TIMING REQUIREMENTS

tSSYNC

SYNC to rising edge of CLK+ setup time

0.24

ns typ

tHSYNC

SYNC to rising edge of CLK+ hold time

0.40

ns typ

SPI TIMING REQUIREMENTS

tDS

Setup time between the data and the rising edge of SCLK

2

ns min

tDH

Hold time between the data and the rising edge of SCLK

2

ns min

tCLK

Period of the SCLK

40

ns min

tS

Setup time between CSB and SCLK

2

ns min

tH

Hold time between CSB and SCLK

2

ns min

tHIGH

SCLK pulse width high

10

ns min

tLOW

SCLK pulse width low

10

ns min

tEN_SDIO

Time required for the SDIO pin to switch from an input to an output

relative to the SCLK falling edge (not shown in Figure 61)

10

ns min

tDIS_SDIO

Time required for the SDIO pin to switch from an output to an input

relative to the SCLK rising edge (not shown in Figure 61)

10

ns min

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102A28-21PY | CONN RCPT 37POS BOX MNT W/PINS |

| D38999/20FB98PNPC | CONN RCPT 6POS WALL MNT W/PINS |

| MS3102A28-21PX | CONN RCPT 37POS BOX MNT W/PINS |

| AD7875KP | IC ADC 12BIT SAMPLING 5V 28PLCC |

| LTC489IN#PBF | IC LINE RCVR RS485 QUAD 16-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9257BCPZRL7-65 | 功能描述:IC ADC 14BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD9257TCPZ-65-EP | 功能描述:14 Bit Analog to Digital Converter 8 Input 8 Pipelined 64-LFCSP-WQ (9x9) 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 位数:14 采样率(每秒):65M 输入数:8 输入类型:差分 数据接口:LVDS - 串行 配置:S/H-ADC 无线电 - S/H:ADC:1:1 A/D 转换器数:8 架构:管线 参考类型:内部 电压 - 电源,模拟:1.7 V ~ 1.9 V 电压 - 电源,数字:1.7 V ~ 1.9 V 特性:同步采样 工作温度:-55°C ~ 125°C 封装/外壳:64-WFQFN 裸露焊盘 供应商器件封装:64-LFCSP-WQ(9x9) 标准包装:1 |

| AD9258 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9258-105EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9258-125EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

发布紧急采购,3分钟左右您将得到回复。