- 您现在的位置:买卖IC网 > PDF目录4590 > AD9267BCPZRL7 (Analog Devices Inc)IC MOD SIGMA-DELTA DUAL 64LFCSP PDF资料下载

参数资料

| 型号: | AD9267BCPZRL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/24页 |

| 文件大小: | 0K |

| 描述: | IC MOD SIGMA-DELTA DUAL 64LFCSP |

| 标准包装: | 750 |

| 类型: | 三角积分调制器 |

| 应用: | 无线通信系统 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

AD9267

Rev. 0 | Page 18 of 24

In normal operation mode, the analog input can toggle the

OR±x pin for a number of clock cycles as it approaches full

scale. The OR±x pin is a pulse-width modulated (PWM) signal;

therefore, as the analog input increases in amplitude, the

duration of OR±x pin toggling increases. Eventually, when the

OR±x pin is high for an extended period of time, the ADC

overloads; thus, there is little correspondence between analog

input and digital output. In this mode, the duration of the

OR±x pin can be used as a coarse indicator to the signal

amplitude at the input of the ADC. In data valid mode, the

OR±x pin remains high when there are no memory access

operations taking place, such as internal calibration or factory

memory transfer, and the inputs of the ADC are within the

operating range.

In either modes of operation, the AUTORST bit can be enabled

and this automatically resets the modulator in an overload

condition. Because the OR±x signal is a PWM signal and the

toggling of OR±x does not always indicate an overload

condition, the modulator only resets after 16 consecutive clock

cycles where OR±x remains high or if the loop filter becomes

saturated. The OR±x pin remains high until the automatic reset

has completed.

If the AD9267 is used in a system that incorporates automatic

gain control (AGC), the OR±x signals can be used to indicate

that the signal amplitude should be reduced. This may be

particularly effective for use in maximizing the signal dynamic

range if the signal includes high occurrence components that

occasionally exceed full scale by a small amount.

TIMING

The AD9267 provides latched data outputs with a latency of

seven clock cycles. The AD9267 also provides a data clock

output (DCO±) pin intended to assist in capturing the data in

an external register. The data outputs are valid on the rising

edge of DCO±, unless changed by setting Serial Register 0x16[7]

(see the Serial Port Interface (SPI) section). See Figure 2 for a

graphical timing description.

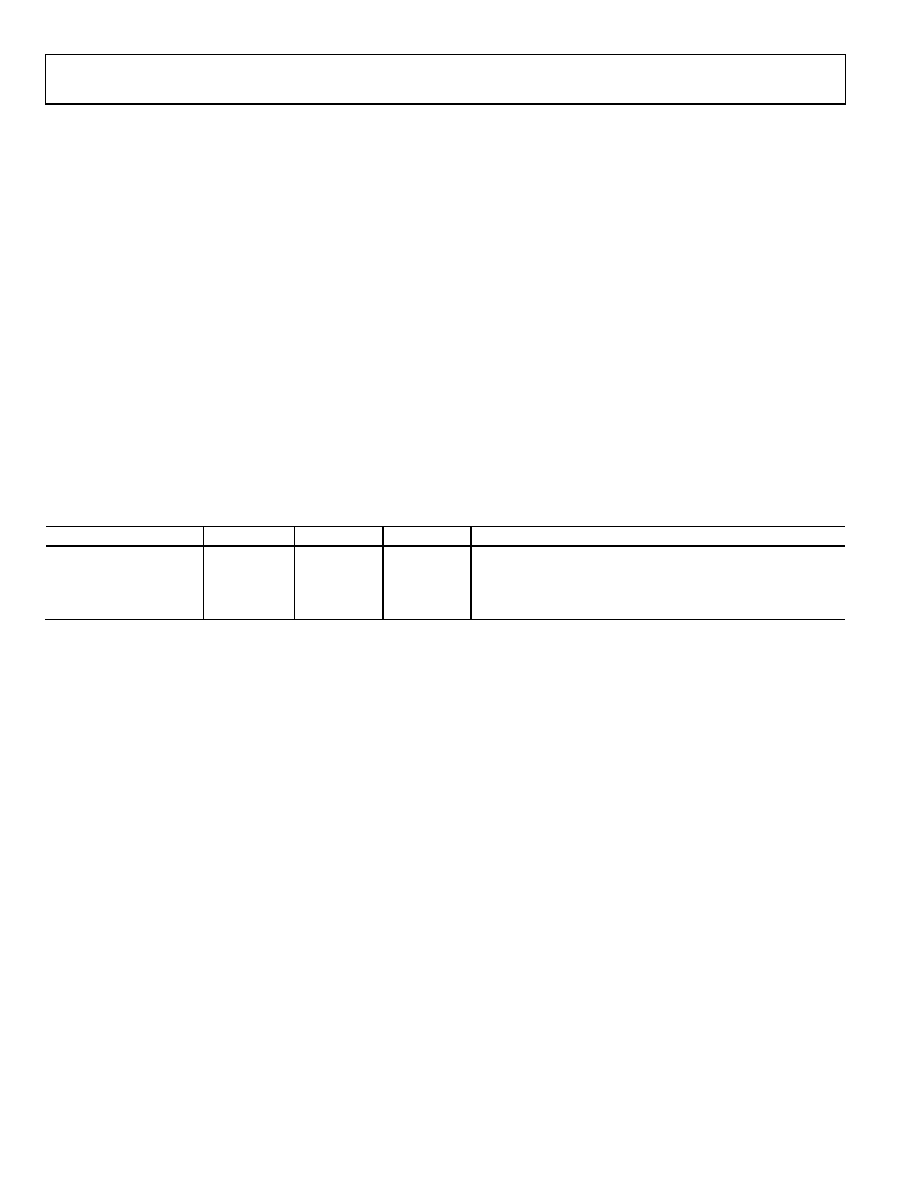

Table 12. OR±x Conditions

Reset State

AUTORST

OR_IND1

OR_IND2

Function

Normal Reset Off

0

If overrange: OR±x = 1, else OR±x = 0

Data Valid Reset Off

0

1

If memory access: OR±x = 0, else OR±x = 1

Normal Reset On

1

0

If overrange or reset: OR±x = 1, else OR±x = 0

Data Valid Reset On

1

If memory access, or reset: OR±x = 0, else OR±x = 1

相关PDF资料 |

PDF描述 |

|---|---|

| LFXP6E-4F256C | IC FPGA 5.8KLUTS 188I/O 256-BGA |

| LFXP6E-3F256I | IC FPGA 5.8KLUTS 188I/O 256-BGA |

| HBC65DRYI | CONN EDGECARD 130PS DIP .100 SLD |

| LFXP6E-4FN256C | IC FPGA 5.8KLUTS 256FPBGA |

| LFXP6E-3FN256I | IC FPGA 5.8KLUTS 188I/O 256-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9267EBZ | 功能描述:BOARD EVALUATION FOR AD9267 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| AD9268 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9268-105EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9268-125EBZ | 功能描述:数据转换 IC 开发工具 Dual 16 bit 125 high SNR ADC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| AD9268-125EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

发布紧急采购,3分钟左右您将得到回复。