- 您现在的位置:买卖IC网 > PDF目录17064 > AD9778A-DPG2-EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9778A PDF资料下载

参数资料

| 型号: | AD9778A-DPG2-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/56页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9778A |

| 标准包装: | 1 |

| 系列: | * |

| DAC 的数量: | 2 |

| 位数: | 14 |

| 采样率(每秒): | 1G |

| 数据接口: | 并联 |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | * |

| 已用 IC / 零件: | AD9778A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9776A/AD9778A/AD9779A

Rev. B | Page 30 of 56

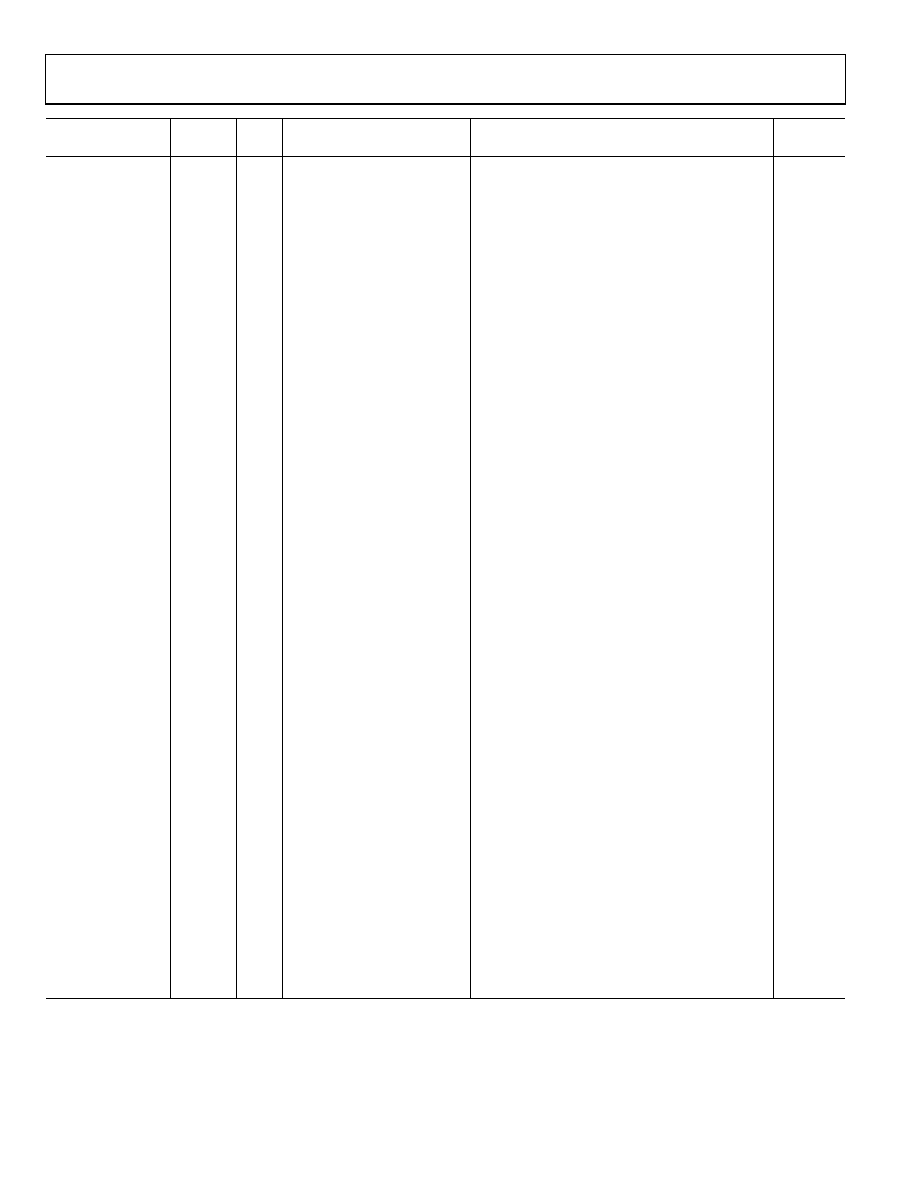

Register

Address

Bits

Register Name

Parameter

Function

Default

Sync Control

0x03

7

DATACLK delay mode

0: manual data timing error detect mode.

1: automatic data timing error detect mode.

0

0x03

6

Reserved

Should always be set to 1.

0

0x03

5:4

DATACLK Divide[1:0]

DATACLK output divider value.

00: divide by 1.

01: divide by 2.

10: divide by 4.

11: divide by 1.

00

0x03

3:0

Data Timing Margin[3:0]

Sets the timing margin required to prevent the

data timing error IRQ bit from being asserted.

0000

0x04

7:4

DATACLK Delay[3:0]

Sets delay of REFCLK input to DATACLK output (see

Table 29 for details).

0000

0x04

3:1

SYNC_O Divide[2:0]

The frequency of the SYNC_O signal is equal to

fDAC/N, where N is set as follows:

000: N = 32.

001: N = 16.

010: N = 8.

011: N = 4.

100: N = 2.

101: N = 1.

110: N = undefined.

111: N = undefined.

000

0x04

0x05

0

7:4

SYNC_O Delay[4]

SYNC_O Delay[3:0]

The SYNC_O Delay[4:0] value programs the value

of the delay line of the SYNC_O signal. The delay of

SYNC_O is relative to REFCLK. The delay line

resolution is 80 ps per step.

00000: nominal delay.

00001: adds 80 ps delay to SYNC_O.

00010: adds 160 ps delay to SYNC_O.

…

11111: Adds 2480 ps delay to SYNC_O.

0

0000

0x05

3:1

SYNC_I Ratio[2:0]

This value controls the number of SYNC_I input

pulses required to generate a synchronization

pulse (see Table 30 for details).

000

0x05

0x06

0

7:4

SYNC_I Delay[4]

SYNC_I Delay[3:0]

The SYNC_I Delay[4:0] value programs the value of

the delay line of the SYNC_I signal. The delay line

resolution is 80 ps per step.

00000: nominal delay.

00001: adds 80 ps delay to SYNC_I.

00010: adds 160 ps delay to SYNC_I.

…

11111: adds 2480 ps delay to SYNC_I.

0

0000

0x06

3:0

SYNC_I Timing Margin[3:0]

0000

0x07

7

SYNC_I enable

1: enables the SYNC_I input.

0

0x07

6

SYNC_O enable

1: enables the SYNC_O output.

0

0x07

5

SYNC_O triggering edge

0: SYNC_O changes on REFCLK falling edge.

1: SYNC_O changes on REFCLK rising edge.

0

0x07

4:0

Clock State[4:0]

This value determines the state of the internal

clock generation state machine upon

synchronization.

0

相关PDF资料 |

PDF描述 |

|---|---|

| SDR0403-101KL | INDUCTOR 100UH 10% NON-SHLD SMD |

| AD9776A-DPG2-EBZ | BOARD EVALUATION FOR AD9776A |

| DC1009A-B | BOARD DELTA SIGMA ADC LTC2488 |

| AD9787-DPG2-EBZ | BOARD EVALUATION FOR AD9787 |

| ESA10DTKS | CONN EDGECARD 20POS DIP .125 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9778A-EBZ | 制造商:Analog Devices 功能描述:Dual 12 /14 /16 Bit, 1 GSPS, Digital To Analog Converters Development Kit 制造商:Analog Devices 功能描述:DUAL 14B, 1.0 GSPS TXDAC - Bulk |

| AD9778BSVZ | 功能描述:IC DAC 14BIT DUAL 1GSPS 100TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):* |

| AD9778BSVZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual 12-/14-/16-Bit, 1 GSPS, Digital-to-Analog Converters |

| AD9778BSVZRL | 功能描述:IC DAC 14BIT DUAL 1GSPS 100TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD9778BSVZRL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual 12-/14-/16-Bit, 1 GSPS, Digital-to-Analog Converters |

发布紧急采购,3分钟左右您将得到回复。