- 您现在的位置:买卖IC网 > PDF目录10979 > AD9852ASTZ (Analog Devices Inc)IC DDS SYNTHESIZER CMOS 80-LQFP PDF资料下载

参数资料

| 型号: | AD9852ASTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/52页 |

| 文件大小: | 0K |

| 描述: | IC DDS SYNTHESIZER CMOS 80-LQFP |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 1 |

| 分辨率(位): | 12 b |

| 主 fclk: | 200MHz |

| 调节字宽(位): | 48 b |

| 电源电压: | 3.14 V ~ 3.47 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-LQFP(14x14) |

| 包装: | 托盘 |

| 产品目录页面: | 552 (CN2011-ZH PDF) |

| 配用: | AD9852/PCBZ-ND - BOARD EVAL FOR AD9852 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9852

Rev. E | Page 25 of 52

CLR ACC2

F1

0

FREQUENCY

MODE

TW1

DPW

000 (DEFAULT)

0

RAMP RATE

011 (CHIRP)

I/O UD CLK

00634-043

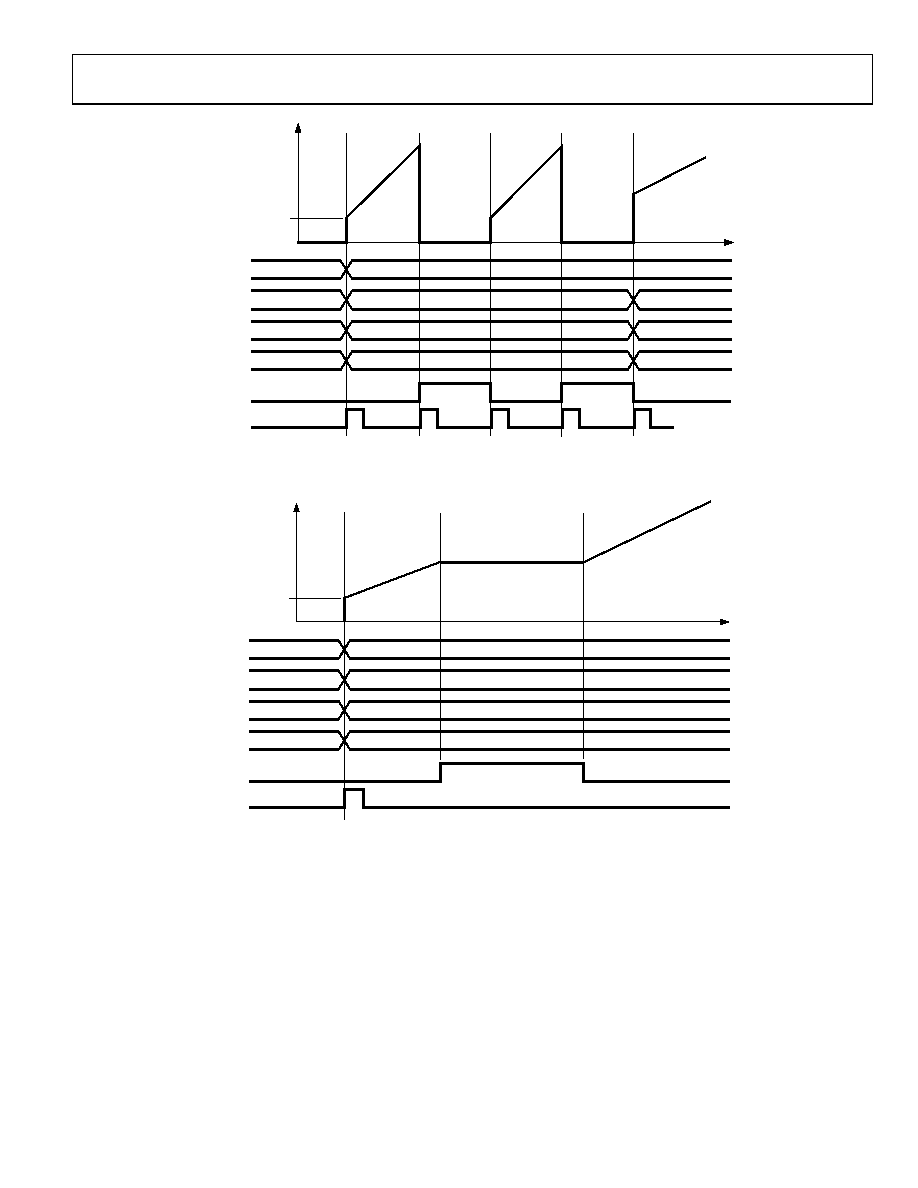

Figure 43. Effect of CLR ACC2 in FM Chirp Mode

HOLD

F1

0

FREQUENCY

MODE

TW1

DFW

000 (DEFAULT)

0

RAMP RATE

011 (CHIRP)

F1

DELTA FREQUENCY WORD

RAMP RATE

I/O UD CLK

00634-044

Figure 44. Example of Hold Function

The 32-bit automatic I/O update counter can be used to

construct complex chirp or ramped FSK sequences. Because

this internal counter is synchronized with the AD9852 system

clock, it allows precisely timed program changes to be invoked.

For such changes, the user need only reprogram the desired

registers before the automatic I/O update clock is generated.

In chirp mode, the destination frequency is not directly speci-

fied. If the user fails to control the chirp, the DDS automatically

confines itself to the frequency range between dc and Nyquist.

Unless terminated by the user, the chirp continues until power

is removed.

When the chirp destination frequency is reached, the user can

choose any of the following actions:

Stop at the destination frequency either by using the

HOLD pin or by loading all 0s into the delta frequency

word registers of the frequency accumulator (ACC1).

Use the HOLD pin function to stop the chirp, and then ramp

down the output amplitude either by using the digital multi-

plier stages and the output shaped keying pin (Pin 30) or by

using the program register control (Address 21 hex to

Address 24 hex).

Abruptly end the transmission with the CLR ACC2 bit.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2WY-IY-F4 | CONVERTER MOD DC/DC 3.3V 33W |

| VE-2WY-IX-F3 | CONVERTER MOD DC/DC 3.3V 49.5W |

| AD9953YSVZ | IC DDS DAC 14BIT 400MSPS 48-TQFP |

| VE-2WX-IY-F4 | CONVERTER MOD DC/DC 5.2V 50W |

| DS3174+ | IC TXRX DS3/E3 QUAD 400-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9852ASTZ | 制造商:Analog Devices 功能描述:IC DDS 100MHZ LQFP-80 |

| AD9852ASTZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:CMOS 300 MSPS Complete DDS |

| AD9852ASVZ | 功能描述:IC DDS SYNTHESIZER CMOS 80-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9852ASVZ | 制造商:Analog Devices 功能描述:IC DDS 300MHz TQFP-80 制造商:Analog Devices 功能描述:IC, DDS, 300MHz, TQFP-80 |

| AD9852ASVZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:CMOS 300 MSPS Complete DDS |

发布紧急采购,3分钟左右您将得到回复。