- 您现在的位置:买卖IC网 > PDF目录10753 > AD9920ABBCZ (Analog Devices Inc)IC PROCESSOR CCD 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9920ABBCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/112页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR CCD 12BIT 105CSPBGA |

| 标准包装: | 1 |

| 位数: | 12 |

| 电压 - 电源,模拟: | 1.6 V ~ 2 V |

| 电压 - 电源,数字: | 1.6 V ~ 2 V |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页

AD9920A

Rev. B | Page 21 of 112

06

87

8-

0

23

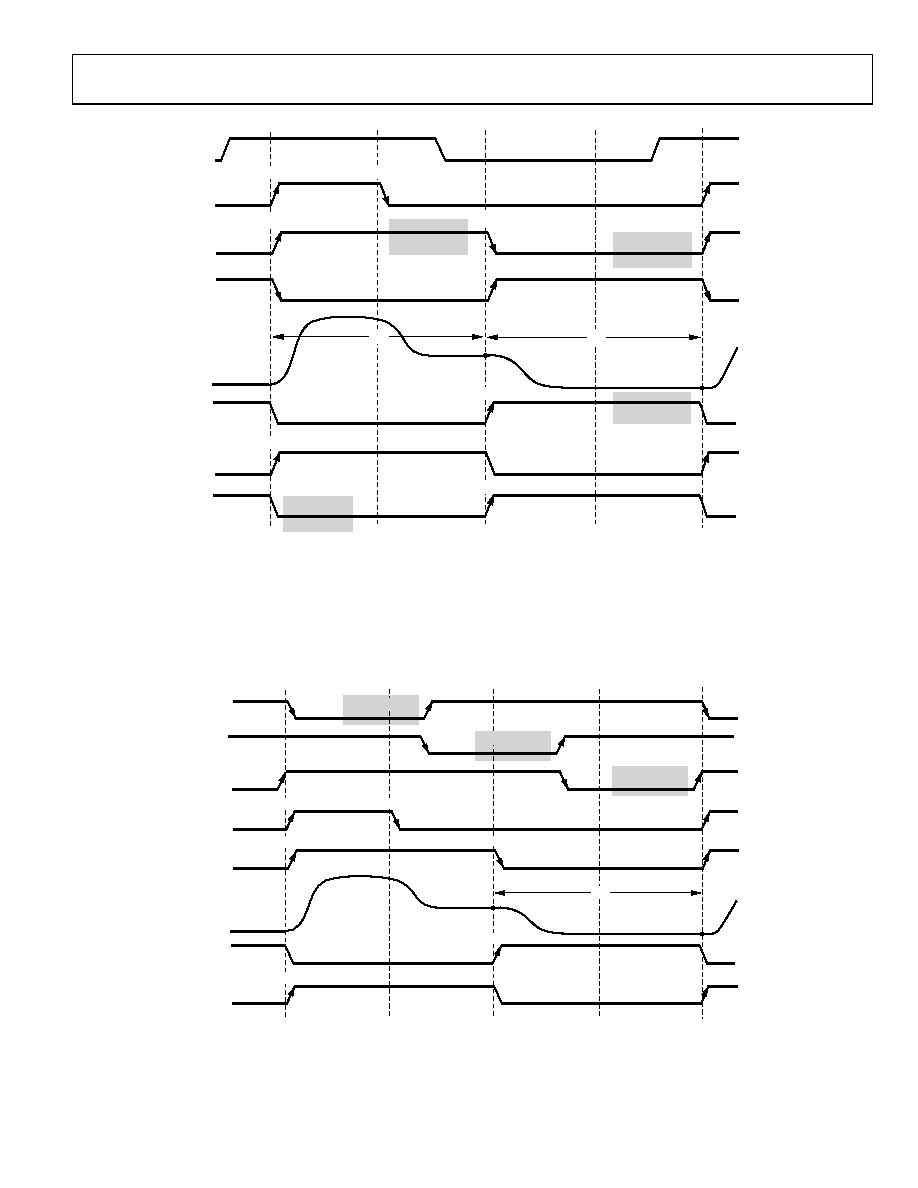

tDOUTINH

tSHPINH

tSHDINH

P[0]

CLI

RG

P[64] = P[0]

CCD

SIGNAL

P[32]

P[16]

P[48]

POSITION

H2

RGr[0]

RGf[16]

SHD

SHDLOC[0]

H1

H1r[0]

H1f[32]

tS1

SHP

SHPLOC[32]

DOUTPHASEP

50

62

1

12

tS2

NOTES

1. ALL SIGNAL EDGES ARE FULLY PROGRAMMABLE TO ANY OF THE 64 POSITIONS WITHIN ONE PIXEL PERIOD.

TYPICAL POSITIONS FOR EACH SIGNAL ARE SHOWN. HCLK MODE 1 IS SHOWN.

2. CERTAIN POSITIONS SHOULD BE AVOIDED FOR EACH SIGNAL, SHOWN ABOVE AS INHIBIT REGIONS.

3. IF A SETTING IN THE INHIBIT REGION IS USED, AN UNSTABLE PIXEL SHIFT CAN OCCUR IN THE HBLK LOCATION OR AFE PIPELINE.

4. THE tSHPINH AREA FROM 50 TO 62 ONLY APPLIES IN SLAVE MODE.

5. THE tSHDINH AREA WILL APPLY TO EITHER H1 RISING OR FALLING EDGE, DEPENDING ON THE VALUE OF THE

H1HBLK MASKING POLARITY.

6. THE tSHDINH AREA CAN ALSO BE CHANGED TO A tSHPINH AREA IF THE H1HBLKRETIME BIT = 1.

Figure 23. High Speed Timing Default Locations

P[0]

RG

P[64] = P[0]

CCD

SIGNAL

P[32]

P[16]

P[48]

TAP POSITION

PHASE 1

RGr[0]

RGf[16]

SHD

SHDLOC[0]

HL

HLr[0]

HLf[32]

tS1

SHP

SHPLOC[32]

PHASE 2

PHASE 3

NOTES

1. ALL SIGNAL EDGES ARE FULLY PROGRAMMABLE TO ANY OF THE 64 POSITIONS WITHIN ONE PIXEL PERIOD.

TYPICAL POSITIONS FOR EACH SIGNAL ARE SHOWN USING 3-PHASE HBLK MODE.

2. THE RISING EDGE OF EACH HCLK PHASE HAS AN ASSOCIATED SHDINH.

3. WHEN THE HBLK RETIME BITS (0x35 [3:0]) ARE ENABLED, THE INHIBITED AREA BECOMES SHPINH.

4. WHEN THE HBLK MASK LEVEL FOR PHASE 1, 2, OR 3 IS CHANGED TO LOW, THE INHIBIT AREA IS

REFERENCED TO THE HCLK FALLING EDGE, INSTEAD OF THE HCLK RISING EDGE.

06

87

8-

0

24

SHDINH/SHPINH

Figure 24. High Speed Timing Typical Locations, 3-Phase HCLK Mode

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LARUZ | IC PROCESSOR FRONTEND DL 28TSSOP |

| V300C2M50BL | CONVERTER MOD DC/DC 2V 50W |

| MAX9025EBT+T | IC COMPARATOR BTR 6-UCSP |

| AD73311LARUZ | IC PROCESSOR FRONT END LP 20SSOP |

| VE-J3F-MY-F1 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9920ABBCZRL | 功能描述:IC PROCESSOR CCD 12BIT 105CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD9920BBCZ | 制造商:Analog Devices 功能描述: |

| AD9920BBCZRL | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9921BBCZ | 制造商:Analog Devices 功能描述: |

| AD9921BBCZRL | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。