- 您现在的位置:买卖IC网 > PDF目录10753 > AD9920ABBCZ (Analog Devices Inc)IC PROCESSOR CCD 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9920ABBCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/112页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR CCD 12BIT 105CSPBGA |

| 标准包装: | 1 |

| 位数: | 12 |

| 电压 - 电源,模拟: | 1.6 V ~ 2 V |

| 电压 - 电源,数字: | 1.6 V ~ 2 V |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页

AD9920A

Rev. B | Page 104 of 112

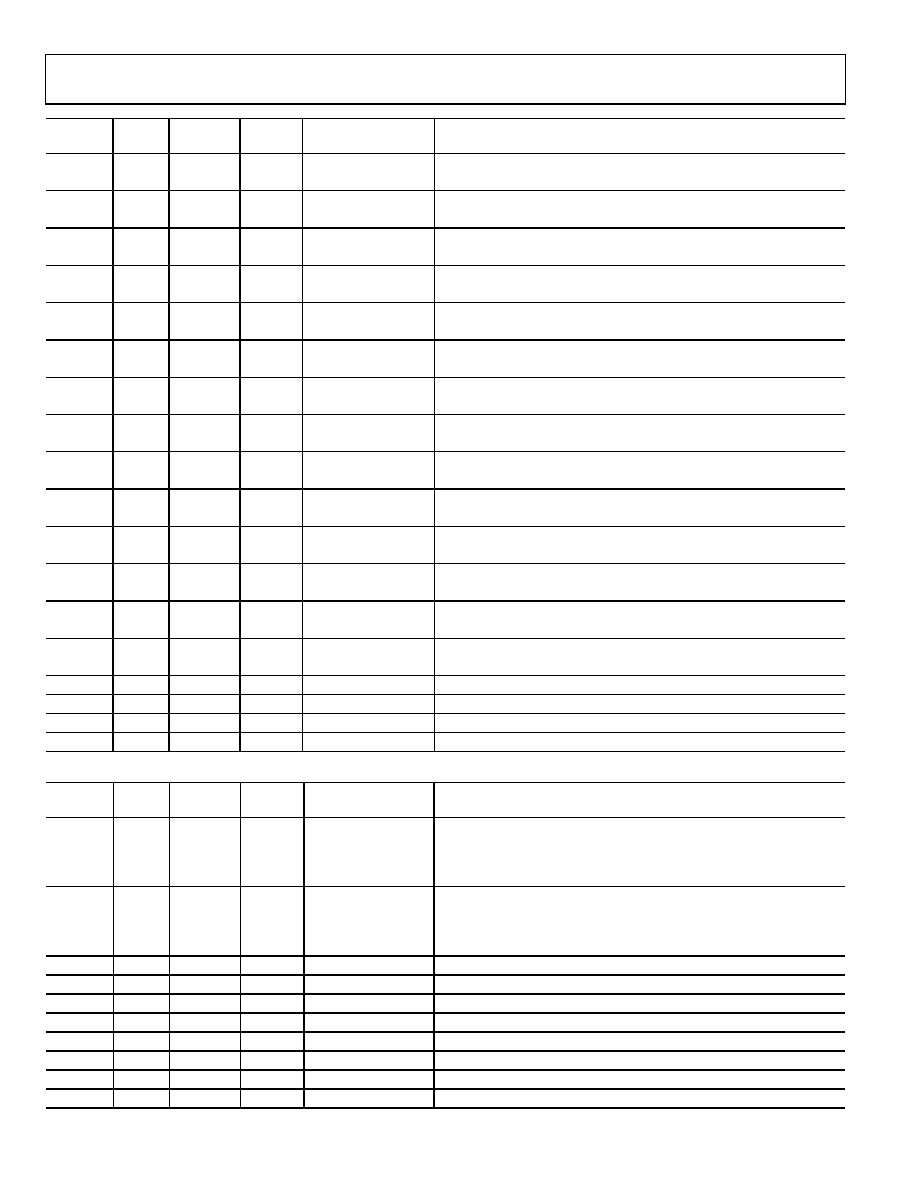

Address

Data

Bits

Default

Value

Update

Type

Name

Description

0x9E

[12:0]

0

VD

GP6_TOG3_PX

General-Purpose Signal 6, third toggle position, pixel location.

[25:13]

0

GP6_TOG4_FD

General-Purpose Signal 6, fourth toggle position, field location.

0x9F

[12:0]

0

VD

GP6_TOG4_LN

General-Purpose Signal 6, fourth toggle position, line location.

[25:13]

0

GP6_TOG4_PX

General-Purpose Signal 6, fourth toggle position, pixel location.

0xA0

[12:0]

0

VD

GP7_TOG1_FD

General-Purpose Signal 7, first toggle position, field location.

[25:13]

0

GP7_TOG1_LN

General-Purpose Signal 7, first toggle position, line location.

0xA1

[12:0]

0

VD

GP7_TOG1_PX

General-Purpose Signal 7, first toggle position, pixel location.

[25:13]

0

GP7_TOG2_FD

General-Purpose Signal 7, second toggle position, field location.

0xA2

[12:0]

0

VD

GP7_TOG2_LN

General-Purpose Signal 7, second toggle position, line location.

[25:13]

0

GP7_TOG2_PX

General-Purpose Signal 7, second toggle position, pixel location.

0xA3

[12:0]

0

VD

GP7_TOG3_FD

General-Purpose Signal 7, third toggle position, field location.

[25:13]

0

GP7_TOG3_LN

General-Purpose Signal 7, third toggle position, line location.

0xA4

[12:0]

0

VD

GP7_TOG3_PX

General-Purpose Signal 7, third toggle position, pixel location.

[25:13]

0

GP7_TOG4_FD

General-Purpose Signal 7, fourth toggle position, field location.

0xA5

[12:0]

0

VD

GP7_TOG4_LN

General-Purpose Signal 7, fourth toggle position, line location.

[25:13]

0

GP7_TOG4_PX

General-Purpose Signal 7, fourth toggle position, pixel location.

0xA6

[12:0]

0

VD

GP8_TOG1_FD

General-Purpose Signal 8, first toggle position, field location.

[25:13]

0

GP8_TOG1_LN

General-Purpose Signal 8, first toggle position, line location.

0xA7

[12:0]

0

VD

GP8_TOG1_PX

General-Purpose Signal 8, first toggle position, pixel location.

[25:13]

0

GP8_TOG2_FD

General-Purpose Signal 8, second toggle position, field location.

0xA8

[12:0]

0

VD

GP8_TOG2_LN

General-Purpose Signal 8, second toggle position, line location.

[25:13]

0

GP8_TOG2_PX

General-Purpose Signal 8, second toggle position, pixel location.

0xA9

[12:0]

0

VD

GP8_TOG3_FD

General-Purpose Signal 8, third toggle position, field location.

[25:13]

0

GP8_TOG3_LN

General-Purpose Signal 8, third toggle position, line location.

0xAA

[12:0]

0

VD

GP8_TOG3_PX

General-Purpose Signal 8, third toggle position, pixel location.

[25:13]

0

GP8_TOG4_FD

General-Purpose Signal 8, fourth toggle position, field location.

0xAB

[12:0]

0

VD

GP8_TOG4_LN

General-Purpose Signal 8, fourth toggle position, line location.

[25:13]

0

GP8_TOG4_PX

General-Purpose Signal 8, fourth toggle position, pixel location.

0xAC

[7:0]

0

VD

GP_LN_MODE

1 = outputs specified GP pulse on every line.

0xAD

[27]

0

VD

UNUSED

Do not access, or set to 0.

0xAE

[27]

0

VD

UNUSED

Do not access, or set to 0.

0xAF

[27]

0

VD

UNUSED

Do not access, or set to 0.

Table 60. Update Control Registers

Address

Data

Bits

Default

Value

Update

Type

Name

Description

0xB0

[15:0]

0x5803

SCK

AFE_UPDT_SCK

Each bit corresponds to one address location.

Bit 0: 1 = update Address 0x00 on SL rising edge.

Bit 1: 1 = update Address 0x01 on SL rising edge.

Bit 15: 1 = update Address 0x0F on SL rising edge.

0xB1

[15:0]

0xA7FC

SCK

AFE_UPDT_VD

Each bit corresponds to one address location.

Bit 0: 1 = update Address 0x00 on VD rising edge.

Bit 1: 1 = update Address 0x01 on VD rising edge.

Bit 15: 1 = update Address 0x0F on VD rising edge.

0xB2

[15:0]

0xD8FD

SCK

MISC_UPDT_SCK

Enable SCK update of miscellaneous registers, Address 0x10 to Address 0x1F.

0xB3

[15:0]

0x2702

SCK

MISC_UPDT_VD

Enable VD update of miscellaneous registers, Address 0x10 to Address 0x1F.

0xB4

[15:0]

0xFFF9

SCK

VDHD_UPDT_SCK

Enable SCK update of VD/HD registers, Address 0x20 to Address 0x2F.

0xB5

[15:0]

0x0006

SCK

VDHD_UPDT_VD

Enable VD update of VD/HD registers, Address 0x20 to Address 0x2F.

0xB6

[15:0]

0xFFFF

SCK

TC_UPDT_SCK

Enable SCK update of timing core registers, Address 0x30 to Address 0x3F.

0xB7

[15:0]

0000

SCK

TC_UPDT_VD

Enable VD update of timing core registers, Address 0x30 to Address 0x3F.

0xB8

[27:0]

0x04

Test

Test register. Do not access, or write to 0x04.

0xB9

[27:0]

0

UNUSED

Do not access, or write to 0x00.

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LARUZ | IC PROCESSOR FRONTEND DL 28TSSOP |

| V300C2M50BL | CONVERTER MOD DC/DC 2V 50W |

| MAX9025EBT+T | IC COMPARATOR BTR 6-UCSP |

| AD73311LARUZ | IC PROCESSOR FRONT END LP 20SSOP |

| VE-J3F-MY-F1 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9920ABBCZRL | 功能描述:IC PROCESSOR CCD 12BIT 105CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD9920BBCZ | 制造商:Analog Devices 功能描述: |

| AD9920BBCZRL | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9921BBCZ | 制造商:Analog Devices 功能描述: |

| AD9921BBCZRL | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。