- 您现在的位置:买卖IC网 > PDF目录10753 > AD9920ABBCZ (Analog Devices Inc)IC PROCESSOR CCD 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9920ABBCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 39/112页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR CCD 12BIT 105CSPBGA |

| 标准包装: | 1 |

| 位数: | 12 |

| 电压 - 电源,模拟: | 1.6 V ~ 2 V |

| 电压 - 电源,数字: | 1.6 V ~ 2 V |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页

AD9920A

Rev. B | Page 32 of 112

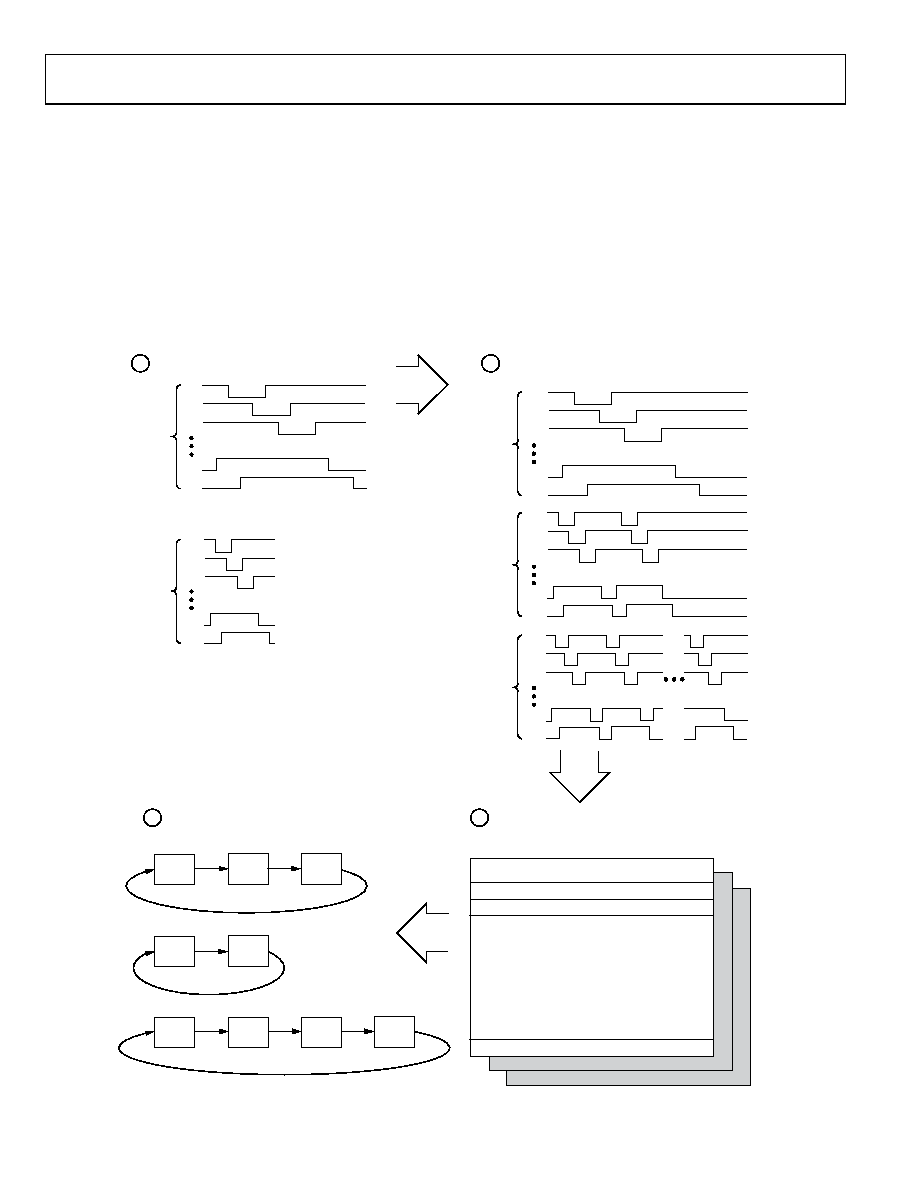

VERTICAL TIMING GENERATION

The AD9920A provides a flexible solution for generating vertical

CCD timing and can support multiple CCDs and different system

architectures. The vertical transfer clocks are used to shift each

line of pixels into the horizontal output register of the CCD. The

AD9920A allows these outputs to be individually programmed

into various readout configurations by using a four-step process.

1.

The individual pulse patterns for XV1 to XV24 are created

by using the vertical pattern group registers.

2.

The V-pattern groups are used to build the V-sequences

where additional information is added.

3.

The readout for an entire field is constructed by dividing

the field into regions and then assigning a sequence to each

region. Each field can contain up to nine different regions

to accommodate the various steps of the readout, such as

high speed line shifts and unique vertical line transfers.

The total number of V-patterns, V-sequences, and fields is

programmable but limited by the number of registers.

4.

The mode registers allow the different fields to be combined

in any order for various readout configurations.

REGION 0: USE V-SEQUENCE 3

REGION 1: USE V-SEQUENCE 2

REGION 2: USE V-SEQUENCE 1

REGION 0: USE V-SEQUENCE 3

REGION 1: USE V-SEQUENCE 2

REGION 2: USE V-SEQUENCE 1

REGION 0: USE V-SEQUENCE 2

REGION 1: USE V-SEQUENCE 0

REGION 3: USE V-SEQUENCE 0

REGION 4: USE V-SEQUENCE 2

XV1

XV2

XV23

XV24

XV1

XV2

XV3

FIELD1

FIELD2

FIELD3

REGION 2: USE V-SEQUENCE 3

FIELD1

FIELD2

FIELD3

FIELD4

FIELD5

FIELD1

FIELD4

FIELD2

XV3

XV23

XV24

VPAT0

XV1

XV2

XV23

XV24

XV3

XV1

XV2

XV23

XV24

XV3

XV1

XV2

XV23

XV24

XV3

VPAT1

1

2

3

4

CREATE THE VERTICAL PATTERN GROUPS,

UP TO FOUR TOGGLE POSITIONS FOR EACH OUTPUT.

BUILD THE V-SEQUENCES BY ADDING START POLARITY,

LINE START POSITION, NUMBER OF REPEATS, ALTERNATION,

GROUP A/B/C/D INFORMATION, AND HBLK/CLPOB PULSES.

V-SEQUENCE 0

(VPAT0, 1 REP)

V-SEQUENCE 1

(VPAT1, 2 REP)

V-SEQUENCE 2

(VPAT1, N REP)

BUILD EACH FIELD BY DIVIDING INTO DIFFERENT REGIONS

AND ASSIGNING A DIFFERENT V-SEQUENCE TO EACH

(MAXIMUM OF NINE REGIONS IN EACH FIELD).

USE THE MODE REGISTERS TO CONTROL WHICH FIELDS

ARE USED AND IN WHAT ORDER (MAXIMUM OF SEVEN

FIELDS CAN BE COMBINED IN ANY ORDER).

06

87

8-

0

40

Figure 41. Summary of Vertical Timing Generation

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LARUZ | IC PROCESSOR FRONTEND DL 28TSSOP |

| V300C2M50BL | CONVERTER MOD DC/DC 2V 50W |

| MAX9025EBT+T | IC COMPARATOR BTR 6-UCSP |

| AD73311LARUZ | IC PROCESSOR FRONT END LP 20SSOP |

| VE-J3F-MY-F1 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9920ABBCZRL | 功能描述:IC PROCESSOR CCD 12BIT 105CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD9920BBCZ | 制造商:Analog Devices 功能描述: |

| AD9920BBCZRL | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9921BBCZ | 制造商:Analog Devices 功能描述: |

| AD9921BBCZRL | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。