参数资料

| 型号: | AD9948KCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/28页 |

| 文件大小: | 0K |

| 描述: | IC CCD SIGNAL PROCESSOR 40-LFCSP |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,10 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

REV. 0

AD9948

–17–

HD

HBLK

. . .

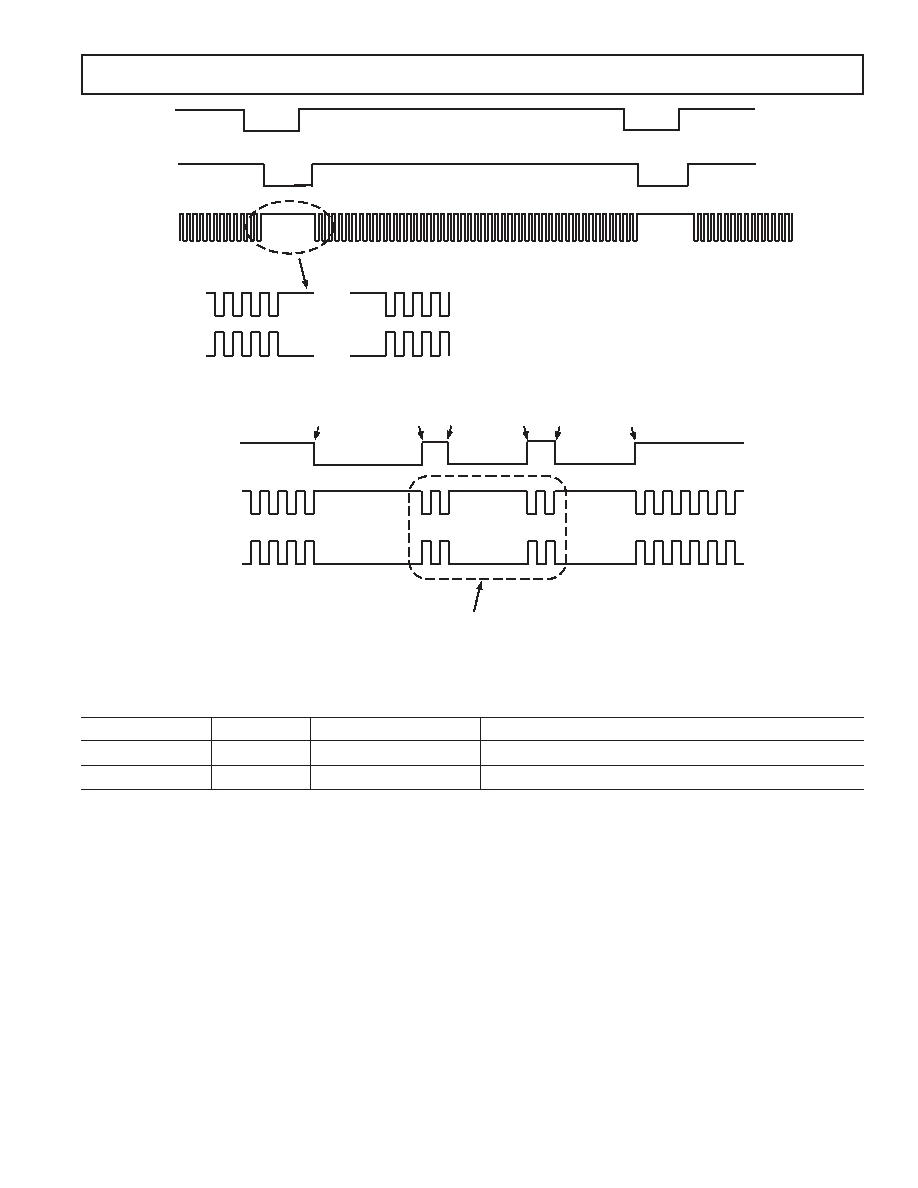

THE POLARITY OF H1 DURING BLANKING IS PROGRAMMABLE (H2 IS OPPOSITE POLARITY OF H1).

. . .

H1/H3

H2/H4

. . .

Figure 10. HBLK Masking Control

HBLK

SPECIAL H-BLANK PATTERN IS CREATED USING MULTIPLE HBLK TOGGLE POSITIONS.

H1/H3

H2/H4

TOG1

TOG2

TOG3

TOG4

TOG5

TOG6

Figure 11. Generating Special HBLK Patterns

GENERATING SPECIAL HBLK PATTERNS

Six toggle positions are available for HBLK. Normally, only

two of the toggle positions are used to generate the standard

HBLK interval. However, the additional toggle positions may be

used to generate special HBLK patterns, as shown in Figure 11.

The pattern in this example uses all six toggle positions to

generate two extra groups of pulses during the HBLK inter-

val. By changing the toggle positions, different patterns can

be created.

Horizontal Sequence Control

The AD9948 uses sequence change positions (SCPs) and sequence

pointers (SPTRs) to organize the individual horizontal sequences.

Up to four SCPs are available to divide the readout into four

separate regions, as shown in Figure 12. The SCP 0 is always hard-

coded to Line 0, and SCP1–SCP3 are register programmable.

During each region bounded by the SCP, the SPTR registers

designate which sequence is used by each signal. CLPOB, PBLK,

and HBLK each have a separate set of SCPs. For example,

CLPOBSCP1 will define Region 0 for CLPOB, and in that region,

any of the four individual CLPOB sequences may be selected with

the CLPOBSPTR register. The next SCP defines a new region,

and in that region each signal can be assigned to a different

individual sequence. The sequence control registers are sum-

marized in Table XIV.

External HBLK Signal

The AD9948 can also be used with an external HBLK signal. Set-

ting the HBLKDIR register (Address x040) to high will disable the

internal HBLK signal generation. The polarity of the external

signal is specified using the HBLKPOL register, and the mask-

ing polarity of H1 is specified using the HBLKMASK register.

Table XV summarizes the register values when using an external

HBLK signal.

Table XIV. Horizontal Sequence Control Parameters for CLPOB, PBLK, and HBLK

Register

Length

Range

Description

SCP

12b

0–4095 Line Number

CLOB/PBLK/HBLK SCP to Define Horizontal Regions 0–3.

SPTR

2b

0–3 Sequence Number

Sequence Pointer for Horizontal Regions 0–3.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9949KCPZ | IC CCD SIGNAL PROCESSOR 40-LFCSP |

| AD9951YSVZ | IC DDS DAC 14BIT 1.8V 48-TQFP |

| AD9952YSVZ-REEL7 | IC DDS DAC 14BIT 1.8V 48TQFP |

| AD9953YSVZ-REEL7 | IC DDS DAC 14BIT 1.8V 48TQFP |

| AD9954YSVZ-REEL7 | IC DDS DAC 14BIT 1.8V 48TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9948KCPZRL | 功能描述:IC CCD SIGNAL PROCESSOR 40-LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD9949 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Bit CCD Signal Processor with Precision Timing Core |

| AD9949AKCPZ | 功能描述:IC CCD SIGNAL PROCESSOR 40-LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD9949AKCPZRL | 功能描述:IC CCD SIGNAL PROCESSOR 40-LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD9949BCBZRL | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。