- 您现在的位置:买卖IC网 > PDF目录10978 > AD9954YSVZ (Analog Devices Inc)IC DDS DAC 14BIT 1.8V 48-TQFP PDF资料下载

参数资料

| 型号: | AD9954YSVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/40页 |

| 文件大小: | 0K |

| 描述: | IC DDS DAC 14BIT 1.8V 48-TQFP |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 1 |

| 分辨率(位): | 14 b |

| 主 fclk: | 400MHz |

| 调节字宽(位): | 32 b |

| 电源电压: | 1.71 V ~ 1.96 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP 裸露焊盘 |

| 供应商设备封装: | 48-TQFP 裸露焊盘(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 552 (CN2011-ZH PDF) |

| 配用: | AD9954/PCBZ-ND - BOARD EVAL FOR 9954 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

AD9954

Rev. B | Page 25 of 40

until the final four bytes are written into the address specified as

the beginning address. When in LSB first mode, the first data

byte is for the least significant byte of the memory (specified by

the beginning address) with the remaining three bytes making

up the greater significant bytes of that address. The remaining

bytes come in least significant to most significant, destined for

RAM addresses generated in ascending order until the final

four bytes are written into the memory address described by the

final address.

The RAM uses Serial Address 01011(b); therefore, the

instruction byte to write the RAM is 0x0B, in MSB first notation.

As previously mentioned, the RAM addresses generated are

specified by the beginning and final address of the RSCW

currently selected by Pin PS1 and Pin PS0.

Notes on serial port operation

The configuration changes made using CFR1<9:8> are

implemented immediately upon writing to this register. For

multibyte transfers, writing to this register may occur during

the middle of a communication cycle. Care must be taken to

compensate for this new configuration for the remainder of

the current communication cycle.

The system must maintain synchronization with the AD9954

or the internal control logic cannot recognize further

instructions. For example, if the system sends an instruction

byte that describes writing a 2-byte register, and then pulses

the SCLK pin for a 3-byte write (24 additional SCLK rising

edges), communication synchronization is lost. In this case,

the first 16 SCLK rising edges after the instruction cycle

properly write the first two data bytes into the AD9954, but

the next eight rising SCLK edges are interpreted as the next

instruction byte. In the case where synchronization is lost

between the system and the AD9954, the IOSYNC pin

enables the user to reset the AD9954 serial port controller

state machine. Any information that is written to the AD9954

registers during a valid communication cycle prior to loss of

synchronization and assertion of the IOSYNC pin remain intact.

Reading a RAM profile requires that the profile select pins,

Pin PS1 and Pin PS0, be configured to select the desired profile.

When reading a register that resides in one of the profiles, the

register address acts as an offset to select one of the registers

among the group of registers defined by the profile, while the

profile select pins select the appropriate register group.

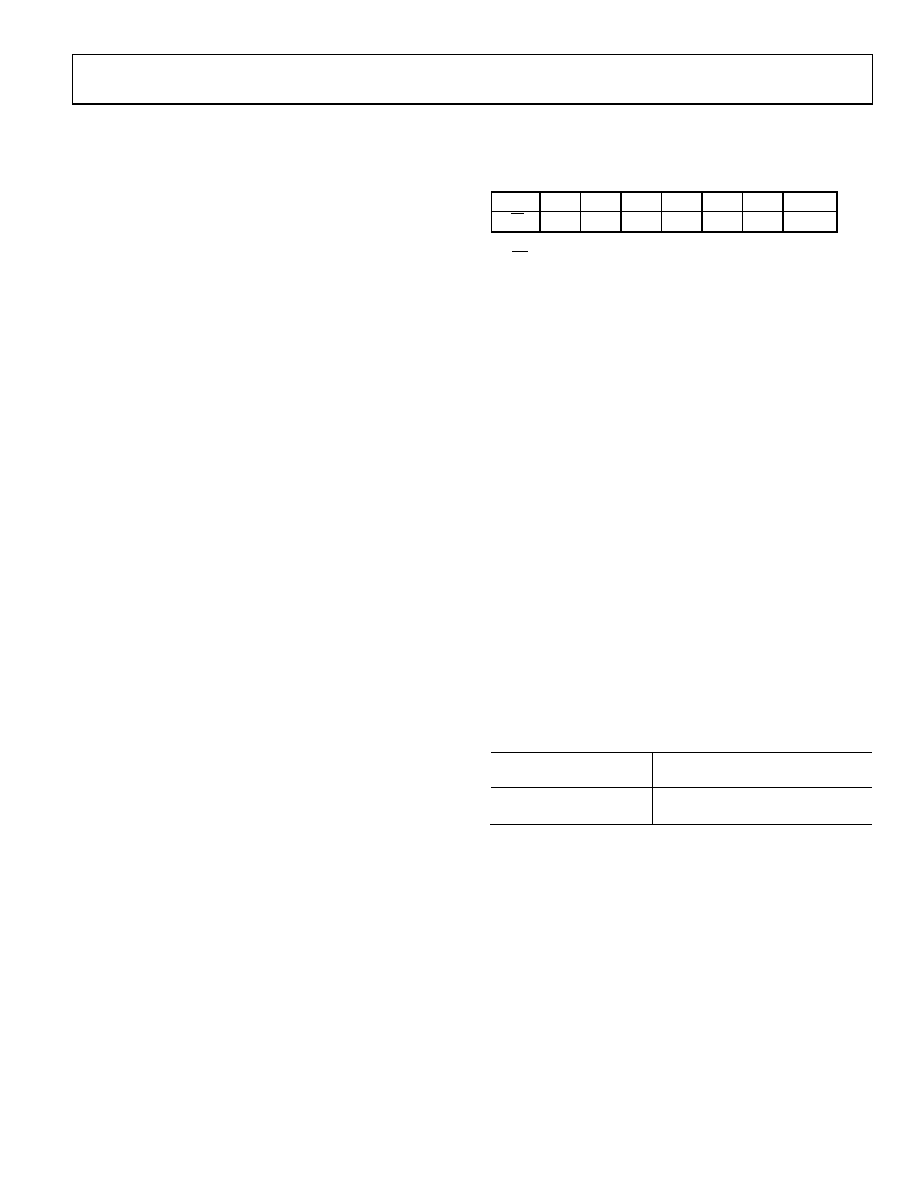

INSTRUCTION BYTE

The instruction byte contains the following information.

Table 10.

MSB

D6

D5

D4

D3

D2

D1

LSB

R/W

X

A4

A3

A2

A1

A0

R/W—Bit 7 of the instruction byte defines whether a read or

write data transfer occurs after the instruction byte write. Logic

High indicates read operation. Logic 0 indicates a write

operation.

X, X—Bit 6 and Bit 5 of the instruction byte are don’t care.

A4, A3, A2, A1, A0—Bit 4, Bit 3, Bit 2, Bit 1, Bit 0 of the

instruction byte determine which register is accessed during the

data transfer portion of the communications cycle. Addresses for

registers can be found in the first column of the register maps (see

REGISTER MAPS AND DESCRIPTIONS

The register maps are listed in Table 12 and Table 13. The active

register map depends on the state of the linear sweep enable bit;

certain registers are remapped depending on which mode the

part is operating in. Specifically, Register 0x07, Register 0x08,

Register 0x09, and Register 0x0A are affected. Because the

linear sweep operation takes precedence over RAM operations,

Analog Devices, Inc. recommends that the RAM be disabled

using Bit CFR1<31> when linear sweep is enabled by Bit

CFR1<21> to conserve power. The serial address numbers

associated with each of the registers are in hexadecimal format.

Angle brackets <> are used to reference specific bits or ranges of

bits. For example, <3> designates Bit 3 and <7:3> designates the

range of bits from Bit 7 to Bit 3, inclusive.

Table 11. Register Mapping Based on Linear Sweep Enable Bit

Linear Sweep Enable Bit

(CFR1<21>)

Register Map

Cleared (= 0)

RAM Segment Control Words Active

Set (= 1)

Linear Sweep Control Words Active

相关PDF资料 |

PDF描述 |

|---|---|

| AD9911BCPZ | IC DDS 500MSPS DAC 10BIT 56LFCSP |

| VE-B11-IY-F4 | CONVERTER MOD DC/DC 12V 50W |

| VE-B11-IY-F1 | CONVERTER MOD DC/DC 12V 50W |

| VE-2WZ-IY-F4 | CONVERTER MOD DC/DC 2V 20W |

| VE-2WZ-IY-F1 | CONVERTER MOD DC/DC 2V 20W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9954YSVZ | 制造商:Analog Devices 功能描述:IC DDS 400MSPS SMD 9954 TQFP48 |

| AD9954YSVZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:400 MSPS, 14-Bit, 1.8 V CMOS, Direct Digital Synthesizer |

| AD9954YSVZ-REEL7 | 功能描述:IC DDS DAC 14BIT 1.8V 48TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD9954YSVZ-REEL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:400 MSPS, 14-Bit, 1.8 V CMOS, Direct Digital Synthesizer |

| AD9955KS6 | 制造商:AD 功能描述:* |

发布紧急采购,3分钟左右您将得到回复。