- 您现在的位置:买卖IC网 > PDF目录11768 > AD9983AKCPZ-140 (Analog Devices Inc)IC INTRFACE 8BIT 140MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9983AKCPZ-140 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 25/44页 |

| 文件大小: | 0K |

| 描述: | IC INTRFACE 8BIT 140MSPS 64LFCSP |

| 标准包装: | 1 |

| 应用: | 视频 |

| 接口: | 模拟 |

| 电源电压: | 1.7 V ~ 3.47 V |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 管件 |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD9983A

Rev. 0 | Page 31 of 44

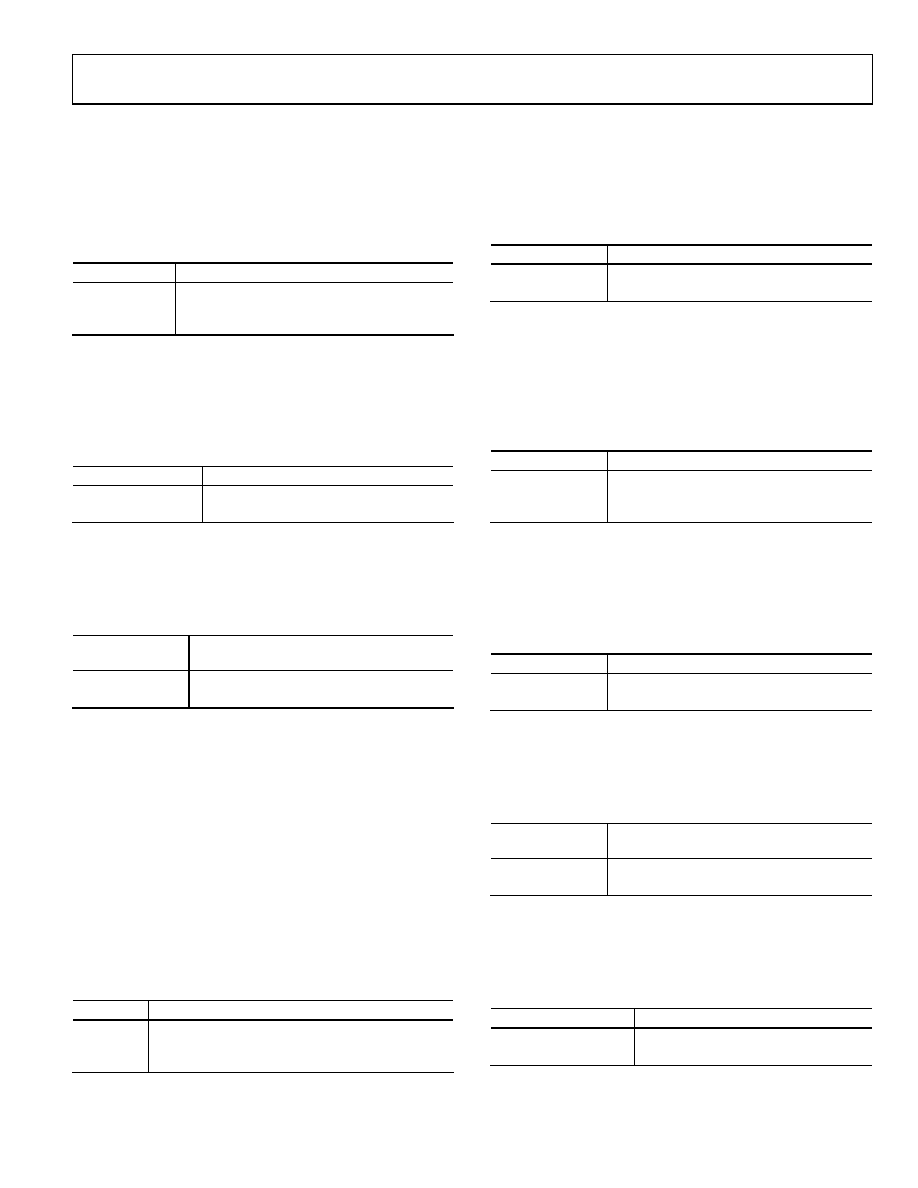

0x12—Bit[5] Hsync Input Polarity Override

This bit determines whether the chip selects the Hsync input

polarity or if it is specified. Setting this bit to 0 allows the chip

to automatically select the polarity of the input Hsync; setting it

to 1 indicates that Bit 4 of Register 0x12 specifies the polarity.

Power-up default is 0.

Table 20. Hsync Input Polarity Override Settings

Override Bit

Result

0

Hsync polarity determined by chip

1

Hsync polarity determined by user

Register 0x12, Bit 4

0x12—Bit[4] Hsync Input Polarity

If Bit 5 of Register 0x12 is 1, the value of this bit specifies the

polarity of the input Hsync. Setting this bit to 0 indicates an

active low Hsync; setting this bit to 1 indicates an active high

Hsync. Power-up default is 1.

Table 21. Hsync Input Polarity Settings

Hsync Polarity Bit

Result

0

Hsync input polarity is negative

1

Hsync input polarity is positive

0x12—Bit[3] Hsync Output Polarity

This bit sets the polarity of the Hsync output. Setting this bit to

0 sets the Hsync output to active low. Setting this bit to 1 sets

the Hsync output to active high. Power-up default setting is 1.

Table 22. Hsync Output Polarity Settings

Hsync Output

Polarity Bit

Result

0

Hsync output polarity is negative

1

Hsync output polarity is positive

0x13—Bits[7:0] Hsync Duration

An 8-bit register that sets the duration of the Hsync output

pulse. The leading edge of the Hsync output is triggered by the

internally-generated, phase-adjusted PLL feedback clock. The

AD9983A then counts a number of pixel clocks equal to the

value in this register. This triggers the trailing edge of the Hsync

output, which is also phase-adjusted.

VSYNC CONTROLS

0x14—Bit[7] Vsync Source Override

This is the active Vsync override. Setting this to 0 allows the

chip to determine the active Vsync source, setting it to 1 uses

Bit 6 of Register 0x14 to determine the active Vsync source.

Power-up default value is 0.

Table 23. Active Vsync Source Override

Override

Result

0

Vsync source determined by chip

1

Vsync source determined by user

Register 0x14, Bit 6

0x14—Bit[6] Vsync Source

This bit selects the source of the Vsync for sync processing only

if Bit 7 of Register 0x14 is set to 1. Setting Bit 6 to 0 specifies the

Vsync from the input pin; setting it to 1 selects Vsync from the

sync separator. Power-up default is 0.

Table 24. Active Vsync Select Settings

Select

Result

0

Vsync input

1

Vsync from sync separator

0x14—Bit[5] Vsync Input Polarity Override

This bit sets whether the chip selects the Vsync input polarity or

if it is specified. Setting this bit to 0 allows the chip to

automatically select the polarity of the input Vsync. Setting this

bit to 1 indicates that Bit 4 of Register 0x14 specifies the

polarity. Power-up default is 0.

Table 25. Vsync Input Polarity Override Settings

Override Bit

Result

0

Vsync polarity determined by chip

1

Vsync polarity determined by user

Register 0x14, Bit 4

0x14—Bit[4] Vsync Input Polarity

If Bit 5 of Register 0x14 is 1, the value of this bit specifies the

polarity of the input Vsync. Setting this bit to 0 indicates an

active low Vsync; setting this bit to 1 indicates an active high

Vsync. Power-up default is 1.

Table 26. Vsync Input Polarity Settings

Override Bit

Result

0

Vsync input polarity is negative

1

Vsync input polarity is positive

0x14—Bit[3] Vsync Output Polarity

This bit sets the polarity of the Vsync output. Setting this bit to

0 sets the Vsync output to active low. Setting this bit to 1 sets

the Vsync output to active high. Power-up default is 1.

Table 27. Vsync Output Polarity Settings

Vsync Output

Polarity Bit

Result

0

Vsync output polarity is negative

1

Vsync output polarity is positive

0x14—Bit[2] Vsync Filter Enable

This bit enables the Vsync filter allowing precise placement of

the Vsync with respect to the Hsync and facilitating the correct

operation of the Hsyncs/Vsync count.

Table 28. Vsync Filter Enable

Vsync Filter Bit

Result

0

Vsync filter disabled

1

Vsync filter enabled

相关PDF资料 |

PDF描述 |

|---|---|

| V150B24H150BG | CONVERTER MOD DC/DC 24V 150W |

| 5227079-5 | CONN PLUG BNC RG58 CRIMP AU |

| VE-JTM-IW-F1 | CONVERTER MOD DC/DC 10V 100W |

| VE-JT1-IW-F4 | CONVERTER MOD DC/DC 12V 100W |

| MS27474E14B35SD | CONN RCPT 37POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9983AKCPZ-1401 | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance 8-Bit Display Interface |

| AD9983AKCPZ-170 | 功能描述:IC INTRFACE 8BIT 170MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD9983AKCPZ-1701 | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance 8-Bit Display Interface |

| AD9983AKSTZ-140 | 功能描述:IC DISPLAY 8BIT 140MSPS 80LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD9983AKSTZ-1401 | 制造商:AD 制造商全称:Analog Devices 功能描述:High Performance 8-Bit Display Interface |

发布紧急采购,3分钟左右您将得到回复。