- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1401AWBSTZ-RL (Analog Devices Inc)IC AUDIO PROC 28/56BIT 48LQFP PDF资料下载

参数资料

| 型号: | ADAU1401AWBSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 33/52页 |

| 文件大小: | 0K |

| 描述: | IC AUDIO PROC 28/56BIT 48LQFP |

| 标准包装: | 2,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 监控器,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

ADAU1401A

Rev. A | Page 39 of 52

ADDRESS 2076 (0x081C)—DSP CORE CONTROL REGISTER

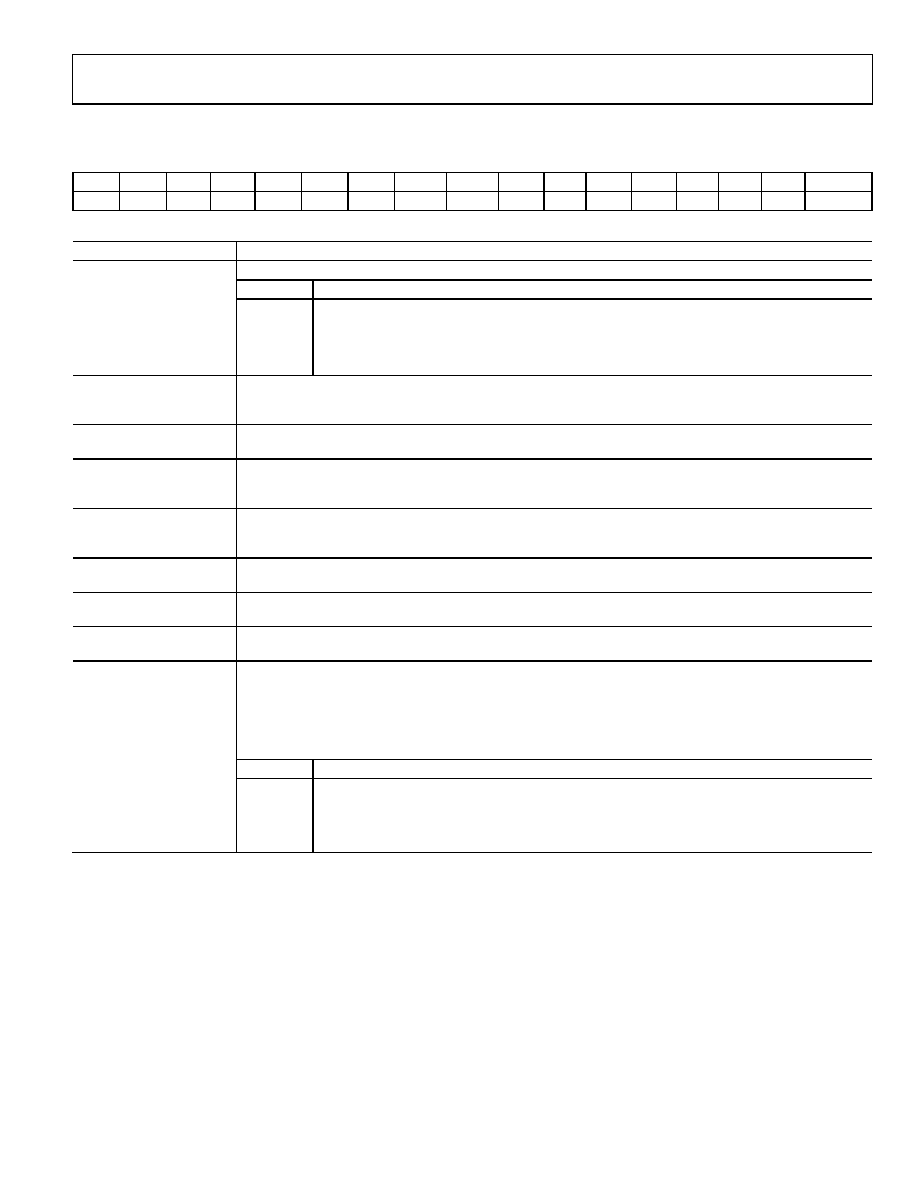

Table 46. DSP Core Control Register Bit Map

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Default

RSVD

GD1

GD0

RSVD

AACW

GPCW

IFCW

IST

ADM

DAM

CR

SR1

SR0

0x0000

Table 47. DSP Core Control Register Bit Descriptions

Bit Name

Description

GPIO debounce control. Sets debounce time of multipurpose pins that are set as GPIO inputs.

Settings

Time (ms)

00

20

01

40

10

GD[1:0]

11

5

AACW

Auxiliary ADC data registers control port write mode. Setting this bit allows data to be written directly to the

auxiliary ADC data registers (Address 2057 to Address 2060) from the control port. When this bit is set, the

auxiliary ADC data registers ignore the settings on the multipurpose pins.

GPCW

GPIO pin setting register control port write mode. When this bit is set, the GPIO pin setting register (Address 2056)

can be written to directly from the control port and this register ignores the input settings on the multipurpose pins.

IFCW

Interface registers control port write mode. When this bit is set, data can be written directly to the interface

registers (Address 2048 to Address 2055) from the control port. In this state, the interface registers are not

written from the SigmaDSP program.

IST

Initiate safeload transfer. Setting this bit to 1 initiates a safeload transfer to the parameter RAM. This bit is

automatically cleared when the operation is complete. There are five safeload register pairs (address/data);

only those registers that have been written since the last safeload event are transferred to the parameter RAM.

ADM

Mute ADCs. This bit mutes the output of the ADCs. The bit defaults to 0 and is active low; therefore, it must be

set to 1 to transmit audio signals from the ADCs.

DAM

Mute DACs. This bit mutes the output of the DACs. The bit defaults to 0 and is active low; therefore, it must be

set to 1 to transmit audio signals from the DACs.

CR

Clear internal registers to 0. This bit defaults to 0 and is active low. It must be set to 1 for a signal to pass

through the SigmaDSP core.

SR[1:0]

Sample rate. These bits set the number of DSP instructions for every sample and the sample rate at which the

ADAU1401A operates. At the default setting of 1×, there are 1024 instructions per audio sample. This setting

should be used with sample rates such as 48 kHz and 44.1 kHz.

At the 2× setting, the number of instructions per frame is halved to 512 and the ADCs and DACs nominally run

at a 96 kHz sample rate.

At the 4× setting, there are 256 instructions per cycle and the converters run at a 192 kHz sample rate.

Settings

Function

00

1× (1024 instructions)

01

2× (512 instructions)

10

4× (256 instructions)

11

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1401YSTZ-RL | IC AUDIO PROC 28/56BIT 48LQFP |

| ADAU1442YSVZ-3A-RL | IC SIGMADSP 28B 175MHZ 100TQFP |

| ADAU1445YSVZ-3A-RL | IC SIGMADSP 175MHZ 100TQFP |

| ADAU1461WBCPZ-R7 | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1401YSTZ | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1401YSTZ-RL | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1421YSTZ | 制造商:Analog Devices 功能描述: |

| ADAU1421YSTZ-REEL | 制造商:Analog Devices 功能描述: |

| ADAU1442 | 制造商:AD 制造商全称:Analog Devices 功能描述:SigmaDSP Digital Audio Processor |

发布紧急采购,3分钟左右您将得到回复。