- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1401AWBSTZ-RL (Analog Devices Inc)IC AUDIO PROC 28/56BIT 48LQFP PDF资料下载

参数资料

| 型号: | ADAU1401AWBSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 35/52页 |

| 文件大小: | 0K |

| 描述: | IC AUDIO PROC 28/56BIT 48LQFP |

| 标准包装: | 2,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 监控器,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

ADAU1401A

Rev. A | Page 40 of 52

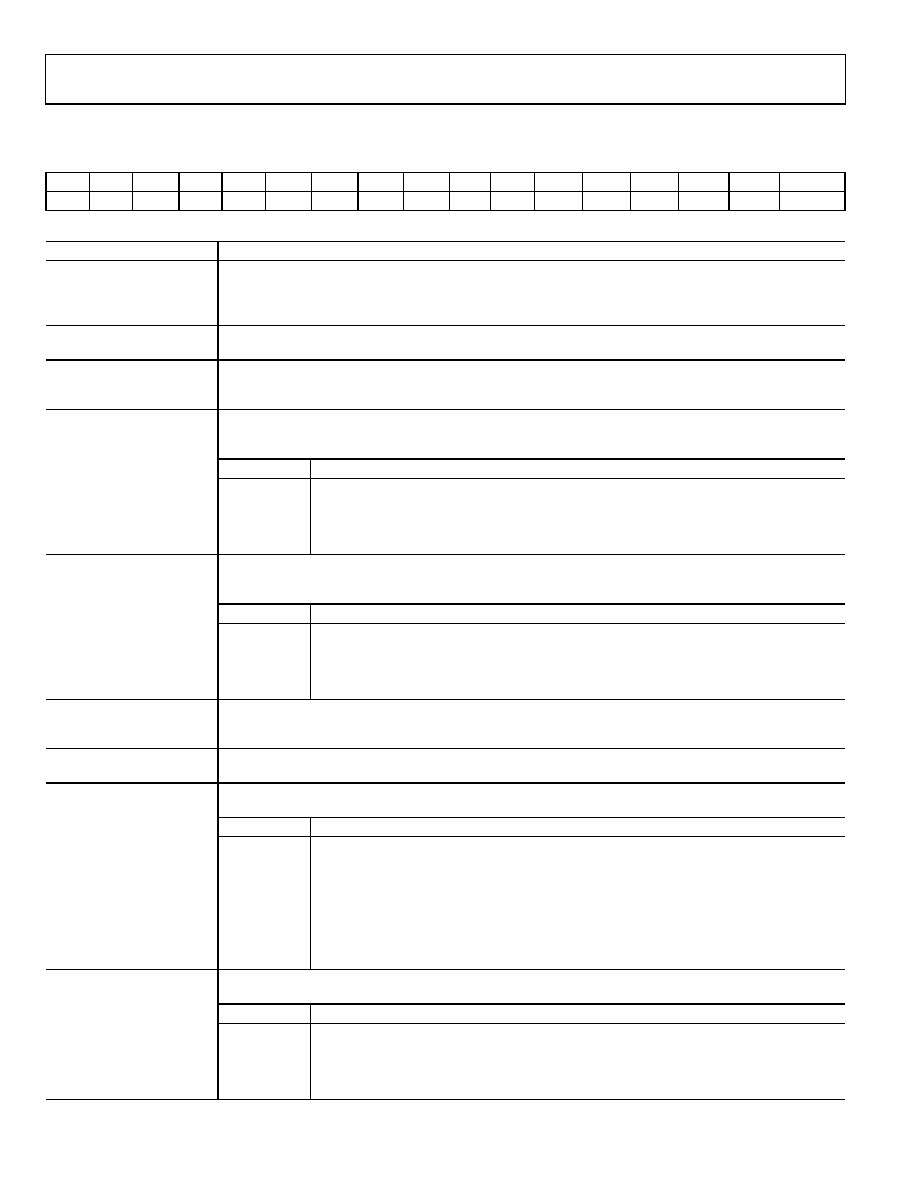

ADDRESS 2078 (0x081E)—SERIAL OUTPUT CONTROL REGISTER

Table 48. Serial Output Control Register Bit Map

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Default

0

OLRP

OBP

M/S

OBF1

OBF0

OLF1

OLF0

FST

TDM

MSB2

MSB1

MSB0

OWL1

OWL0

0x0000

Table 49. Serial Output Control Register Bit Descriptions

Bit Name

Description

OLRP

OUTPUT_LRCLK polarity. When this bit is set to 0, the left-channel data is clocked when OUTPUT_LRCLK is

low and the right-channel data is clocked when OUTPUT_LRCLK is high. When this bit is set to 1, the right-

channel data is clocked when OUTPUT_LRCLK is low and the left-channel data is clocked when

OUTPUT_LRCLK is high.

OBP

OUTPUT_BCLK polarity. This bit controls on which bit clock edge the output data is clocked. Data changes on

the falling edge of OUTPUT_BCLK when this bit is set to 0 and on the rising edge when this bit is set to 1.

M/S

Master/slave. This bit sets whether the output port is a clock master or slave. The default setting is slave; on

power-up, the OUTPUT_BCLK and OUTPUT_LRCLK pins are set as inputs until this bit is set to 1, at which time

they become clock outputs.

OUTPUT_BCLK frequency (master mode only). When the output port is being used as a clock master, these

bits set the frequency of the output bit clock, which is divided down from an internal 1024 × fS clock (49.152

MHz for a fS of 48 kHz).

Settings

Function

00

Internal clock/16

01

Internal clock/8

10

Internal clock/4

OBF[1:0]

11

Internal clock/2

OUTPUT_LRCLK frequency (master mode only). When the output port is used as a clock master, these bits set

the frequency of the output word clock on the OUTPUT_LRCLK pin, which is divided down from an internal

1024 × fS clock (49.152 MHz for a fS of 48 kHz).

Settings

Function

00

Internal clock/1024

01

Internal clock/512

10

Internal clock/256

OLF[1:0]

11

Reserved

FST

Frame sync type. This bit sets the type of signal on the OUTPUT_LRCLK pin. When this bit is set to 0, the signal

is a word clock with a 50% duty cycle; when this bit is set to 1, the signal is a pulse with a duration of one bit

clock at the beginning of the data frame.

TDM

TDM enable. Setting this bit to 1 changes the output port from four serial stereo outputs to a single 8-channel

TDM output stream on the SDATA_OUT0 pin (MP6).

MSB position. These three bits set the position of the data’s MSB with respect to the LRCLK edge. The data

output of the ADAU1401A is always MSB first.

Settings

Function

000

Delay by 1

001

Delay by 0

010

Delay by 8

011

Delay by 12

100

Delay by 16

101

Reserved

MSB[2:0]

111

Reserved

Output word length. These bits set the word length of the output data-word. All bits following the LSB are set

to 0.

Settings

Function

00

24 bits

01

20 bits

10

16 bits

OWL[1:0]

11

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1401YSTZ-RL | IC AUDIO PROC 28/56BIT 48LQFP |

| ADAU1442YSVZ-3A-RL | IC SIGMADSP 28B 175MHZ 100TQFP |

| ADAU1445YSVZ-3A-RL | IC SIGMADSP 175MHZ 100TQFP |

| ADAU1461WBCPZ-R7 | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1401YSTZ | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1401YSTZ-RL | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1421YSTZ | 制造商:Analog Devices 功能描述: |

| ADAU1421YSTZ-REEL | 制造商:Analog Devices 功能描述: |

| ADAU1442 | 制造商:AD 制造商全称:Analog Devices 功能描述:SigmaDSP Digital Audio Processor |

发布紧急采购,3分钟左右您将得到回复。