- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1401YSTZ-RL (Analog Devices Inc)IC AUDIO PROC 28/56BIT 48LQFP PDF资料下载

参数资料

| 型号: | ADAU1401YSTZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 41/52页 |

| 文件大小: | 0K |

| 描述: | IC AUDIO PROC 28/56BIT 48LQFP |

| 标准包装: | 2,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 监控器,电视 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

ADAU1401

Data Sheet

Rev. C | Page 46 of 52

The serial data clocks need to be synchronous with the ADAU1401

master clock input.

The input control register allows control of clock polarity and

data input modes. The valid data formats are I2S, left-justified,

right-justified (24-/20-/18-/16-bit), and 8-channel TDM. In all

modes except for the right-justified modes, the serial port accepts

an arbitrary number of bits up to a limit of 24. Extra bits do not

cause an error, but they are truncated internally. Proper operation

of the right-justified modes requires that there be exactly 64 BCLKs

per audio frame. The TDM data is input on SDATA_IN0. The

LRCLK in TDM mode can be input to the ADAU1401 either as

a 50/50 duty cycle clock or as a bit-wide pulse.

In TDM mode, the ADAU1401 can be a master for 48 kHz and

96 kHz data, but not for 192 kHz data. Table 64 lists the modes

in which the serial output port can function.

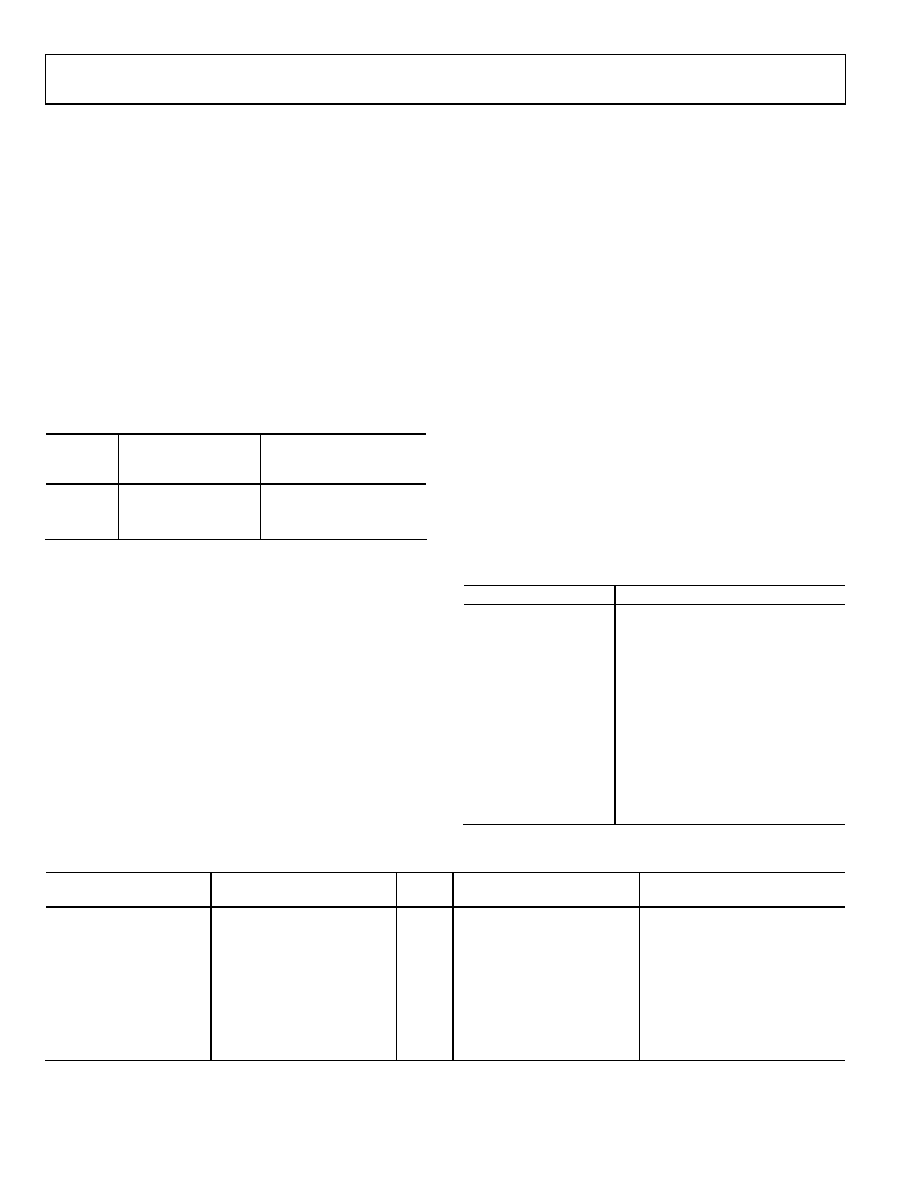

Table 64. Serial Output Port Master/Slave Mode Capabilities

fS

2-Channel Modes

(I2S, Left Justified,

Right Justified)

8-Channel TDM

48 kHz

Master and slave

96 kHz

Master and slave

192 kHz

Master and slave

Slave only

The output control registers allow the user to control clock

polarities, clock frequencies, clock types, and data format. In all

modes except for the right-justified modes (MSB delayed by 8,

12, or 16 bits), the serial port accepts an arbitrary number of

bits up to a limit of 24. Extra bits do not cause an error, but are

truncated internally. Proper operation of the right-justified modes

requires the LSB to align with the edge of the LRCLK. The default

settings of all serial port control registers correspond to 2-channel

I2S mode. All register settings apply to both master and slave

modes unless otherwise noted.

The function of each multipurpose pin in serial data port mode

is shown in Table 65. Pin MP0 to Pin MP5 support digital data

input to the ADAU1401, and Pin MP6 to Pin MP11 handle digital

data output from the DSP. The configuration of the serial data

input port is set in the serial input control register (Table 51), and

the configuration of the corresponding output port is controlled

with the serial output control register (Table 49). The clocks of

the input port function only as slaves, whereas the output port

clocks can be set to function as either masters or slaves. The

INPUT_LRCLK (MP4) and INPUT_BCLK (MP5) pins are

used to clock the SDATA_INx (MP0 to MP3) signals, and the

OUTPUT_LRCLK (MP10) and OUTPUT_BCLK (MP11) pins

are used to clock the SDATA_OUTx (MP6 to MP9) signals.

If an external ADC is connected as a slave to the ADAU1401,

use both the input and output port clocks. The OUTPUT_LRCLK

(MP10) and OUTPUT_BCLK (MP11) pins must be set to master

mode and connected externally to the INPUT_LRCLK (MP4)

and INPUT_BCLK (MP5) pins as well as to the external ADC

clock input pins. The data is output from the external ADC into

the SigmaDSP on one of the four SDATA_INx pins (MP0 to MP3).

Connections to an external DAC are handled exclusively with the

output port pins. The OUTPUT_LRCLK and OUTPUT_BCLK

pins can be set to function as either masters or slaves, and the

SDATA_OUTx pins are used to output data from the SigmaDSP

to the external DAC.

Table 66 describes the proper configurations for standard audio

data formats.

Table 65. Multipurpose Pin Serial Data Port Functions

Multipurpose Pin

Function

MP0

SDATA_IN0/TDM_IN

MP1

SDATA_IN1

MP2

SDATA_IN2

MP3

SDATA_IN3

MP4

INPUT_LRCLK (slave only)

MP5

INPUT_BCLK (slave only)

MP6

SDATA_OUT0/TDM_OUT

MP7

SDATA_OUT1

MP8

SDATA_OUT2

MP9

SDATA_OUT3

MP10

OUTPUT_LRCLK (master or slave)

MP11

OUTPUT_BCLK (master or slave)

Table 66. Data Format Configurations

Format

LRCLK Polarity

LRCLK

Type

BCLK Polarity

MSB Position

Frame begins on falling edge

Clock

Data changes on falling edge

Delayed from LRCLK edge

by 1 BCLK

Left-Justified (Figure 33)

Frame begins on rising edge

Clock

Data changes on falling edge

Aligned with LRCLK edge

Right-Justified (Figure 34)

Frame begins on rising edge

Clock

Data changes on falling edge

Delayed from LRCLK edge

by 8, 12, or 16 BCLKs

TDM with Clock (Figure 35)

Frame begins on falling edge

Clock

Data changes on falling edge

Delayed from start of word clock

by 1 BCLK

TDM with Pulse (Figure 36)

Frame begins on rising edge

Pulse

Data changes on falling edge

Delayed from start of word clock

by 1 BCLK

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1442YSVZ-3A-RL | IC SIGMADSP 28B 175MHZ 100TQFP |

| ADAU1445YSVZ-3A-RL | IC SIGMADSP 175MHZ 100TQFP |

| ADAU1461WBCPZ-R7 | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

| ADAU1590ACPZ-RL7 | IC AMP AUDIO PWR 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1421YSTZ | 制造商:Analog Devices 功能描述: |

| ADAU1421YSTZ-REEL | 制造商:Analog Devices 功能描述: |

| ADAU1442 | 制造商:AD 制造商全称:Analog Devices 功能描述:SigmaDSP Digital Audio Processor |

| ADAU1442YSVZ-3A | 功能描述:IC SIGMADSP 28B 175MHZ 100TQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1442YSVZ-3A-RL | 功能描述:IC SIGMADSP 28B 175MHZ 100TQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

发布紧急采购,3分钟左右您将得到回复。