- 您现在的位置:买卖IC网 > PDF目录10735 > ADCMP572BCPZ-WP (Analog Devices Inc)IC COMPARATOR CML 3.3-5V 16LFCSP PDF资料下载

参数资料

| 型号: | ADCMP572BCPZ-WP |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | IC COMPARATOR CML 3.3-5V 16LFCSP |

| 标准包装: | 50 |

| 类型: | 带锁销 |

| 元件数: | 1 |

| 输出类型: | CML,补充型 |

| 电压 - 电源,单路/双路(±): | 3.1 V ~ 5.4 V |

| 电压 - 输入偏移(最小值): | 2mV @ 3.3V |

| 电流 - 输入偏压(最小值): | 25µA @ 3.3V |

| 电流 - 输出(标准): | 20mA |

| 电流 - 静态(最大值): | 52mA |

| CMRR, PSRR(标准): | 65dB CMRR,74dB PSRR |

| 传输延迟(最大): | 0.165ns |

| 磁滞: | ±1mV |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 16-VFQFN 裸露焊盘,CSP |

| 安装类型: | 表面贴装 |

| 包装: | 托盘 - 晶粒 |

| 配用: | EVAL-ADCMP572BCPZ-ND - BOARD EVALUATION ADCMP572BCP |

ADCMP572/ADCMP573

Rev. A | Page 6 of 16

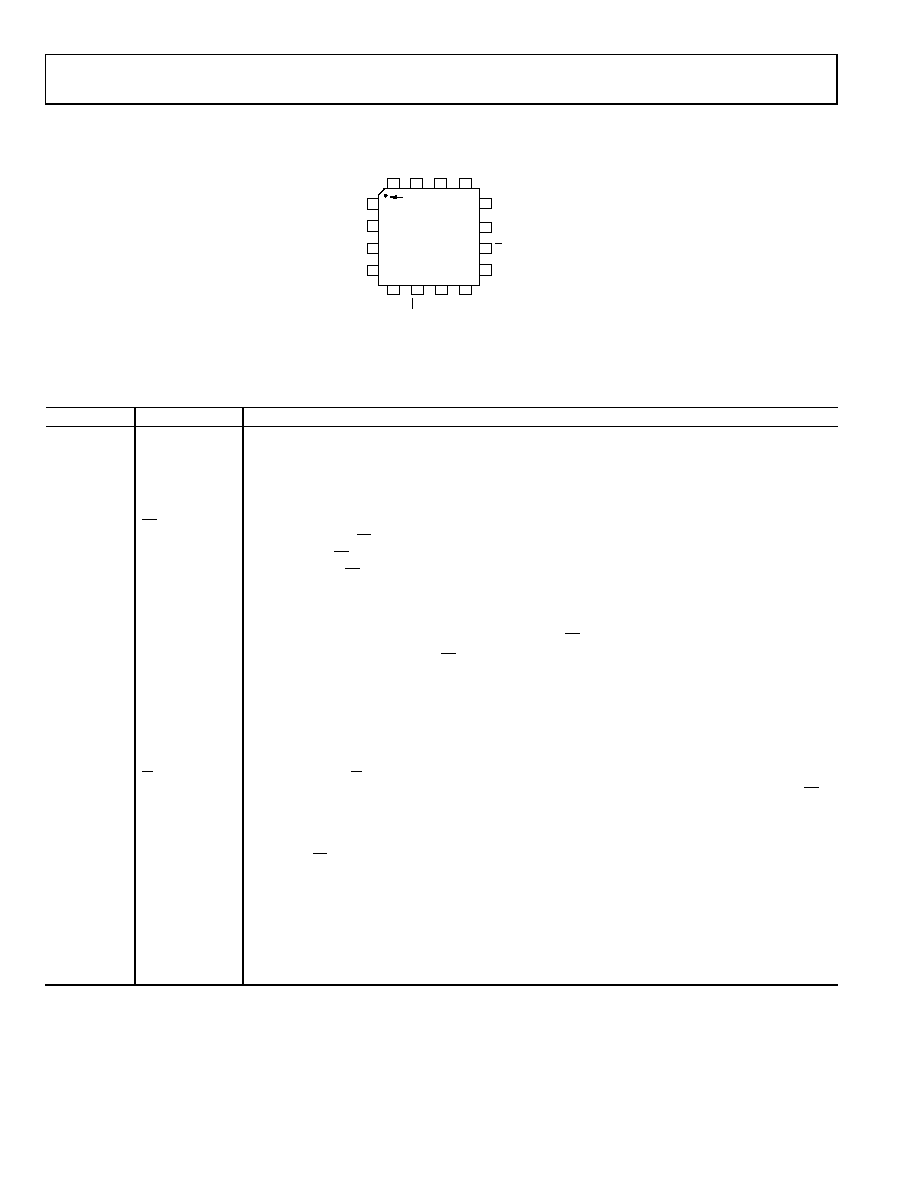

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

04409-026

5

V

CCI

6

LE

7

LE

8

V

CCO

/V

TT

ADCMP572

ADCMP573

TOP VIEW

(Not to Scale)

1

VTP

PIN1

2

VP

3

VN

4

VTN

16

V

CCI

15

GND

14

HY

S

13

GND

VCCO

12

Q

11

Q

10

VCCO

9

Figure 2. ADCMP572/ADCMP573 Pin Configuration

Table 3. Pin Function Descriptions

Pin No.

Mnemonic

Description

1

VTP

Termination Resistor Return Pin for VP Input.

2

VP

Noninverting Analog Input.

3

VN

Inverting Analog Input.

4

VTN

Termination Resistor Return Pin for VN Input.

5, 16

VCCI

Positive Supply Voltage for Input Stage.

6

LE

Latch Enable Input Pin, Inverting Side.

In compare mode (LE = low), the output tracks changes at the input of the comparator.

In latch mode (LE = high), the output reflects the input state just prior to the comparator’s being placed

into latch mode. LE must be driven in complement with LE.

7

LE

Latch Enable Input Pin, Noninverting Side.

In compare mode (LE = high), the output tracks changes at the input of the comparator.

In latch mode (LE = low), the output reflects the input state just prior to the comparator’s being placed

into latch mode. LE must be driven in complement with LE.

8

VCCO/VTT

Termination Return Pin for the LE/LE Input Pins.

For the ADCMP572 (CML output stage), this pin is internally connected to and also should be externally

connected to the positive VCCO supply.

For the ADCMP573 (RSPECL output stage), this pin should normally be connected to the VCCO – 2 V

termination potential.

9, 12

VCCO

Positive Supply Voltage for the CML/RSPECL Output Stage.

13, 15

GND

Ground.

10

Q

Inverting Output. Q is at logic low if the analog voltage at the noninverting input, VP, is greater than the

analog voltage at the inverting input, VN, provided the comparator is in compare mode. See the LE/LE

descriptions (Pins 6 and 7) for more information.

11

Q

Noninverting Output. Q is at logic high if the analog voltage at the noninverting input VP is greater

than the analog voltage at the inverting input, VN, provided the comparator is in compare mode.

See the LE/LE descriptions (Pins 6 and 7) for more information.

14

HYS

Hysteresis Control Pin. Leave this pin disconnected for zero hysteresis. Connect to GND with a suitably

sized resistor to add the desired amount of hysteresis. Refer to Figure 7 for proper sizing of RHYS

hysteresis control resistor.

Isolated

Heat Sink

N/C

The metallic back surface of the package is not electrically connected to any part of the circuit, and it

can be left floating for best electrical isolation between the package handle and the substrate of the

die. However, it can be soldered to the application board if improved thermal and/or mechanical

stability is desired. Exposed metal at package corners is connected to the heat sink paddle.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-J4V-MY-F4 | CONVERTER MOD DC/DC 5.8V 50W |

| VI-JNW-MY-F2 | CONVERTER MOD DC/DC 5.5V 50W |

| VE-2WN-MY-B1 | CONVERTER MOD DC/DC 18.5V 50W |

| VE-2N4-CV-B1 | CONVERTER MOD DC/DC 48V 150W |

| VE-2WM-MY-B1 | CONVERTER MOD DC/DC 10V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADCMP572XCP | 制造商:Analog Devices 功能描述:CML ULTRAFAST 3.3V SINGLE SUPPLY COMPARATOR - Bulk |

| ADCMP573 | 制造商:AD 制造商全称:Analog Devices 功能描述:Ultrafast 3.3 V Single-Supply Comparators |

| ADCMP573BCP | 制造商:Analog Devices 功能描述:COMPARATOR SGL 5.4V 16LFCSP EP - Bulk |

| ADCMP573BCP-R2 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADCMP573BCPRL7 | 制造商:AD 功能描述:NEW |

发布紧急采购,3分钟左右您将得到回复。