- 您现在的位置:买卖IC网 > PDF目录373996 > ADM1069ACP (Analog Devices, Inc.) SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS PDF资料下载

参数资料

| 型号: | ADM1069ACP |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| 中文描述: | 超时序与裕度控制以及辅助ADC输入商标 |

| 文件页数: | 19/32页 |

| 文件大小: | 626K |

| 代理商: | ADM1069ACP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

Preliminary Technical Data

ADM1069

SEQUENCE DETECTOR

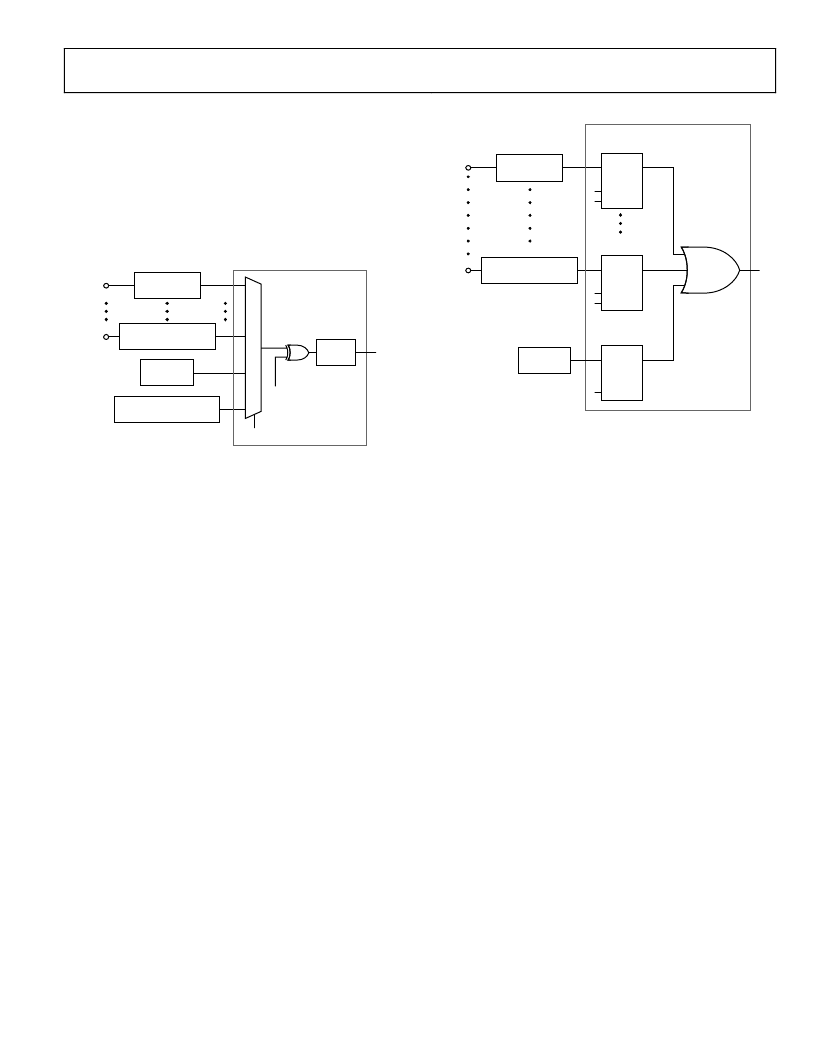

The sequence detector block is used to detect when a step in a

sequence has been completed. It looks for one of the inputs to

the SE to change state, and is most often used as the gate on

successful progress through a power-up or power-down

sequence. A timer block is included in this detector, which

can insert delays into a power-up or power-down sequence,

if required. Timer delays can be set from 10 μs to 400 ms.

Figure 27 is a block diagram of the sequence detector.

Rev. PrB | Page 19 of 32

0

SUPPLY FAULT

DETECTION

LOGIC INPUT CHANGE

OR FAULT DETECTION

WARNINGS

FORCE FLOW

(UNCONDITIONAL JUMP)

VP1

VX4

INVERT

SEQUENCE

DETECTOR

SELECT

TIMER

Figure 27. Sequence Detector Block Diagram

The sequence detector can also help to identify monitoring

faults. In the sample application shown in Figure 26, the FSEL1

and FSEL2 states first identify which of the VP1,VP2, or VP3

pins has faulted, and then they take the appropriate action.

MONITORING FAULT DETECTOR

The monitoring fault detector block is used to detect a failure

on an input. The logical function implementing this is a wide

OR gate, which can detect when an input deviates from its

expected condition. The clearest demonstration of the use of

this block is in the PWRGD state, where the monitor block

indicates that a failure on one or more of the VP1,VP2, or VP3

inputs has occurred.

No programmable delay is available in this block, because the

triggering of a fault condition is likely to be caused when a supply

falls out of tolerance. In this situation, the user would want to

react as quickly as possible. Some latency occurs when moving

out of this state, however, because it takes a finite amount of

time (~20 μs) for the state configuration to download from

EEPROM into the SE. Figure 28 is a block diagram of the

monitoring fault detector.

0

SUPPLY FAULT

DETECTION

LOGIC INPUT CHANGE

OR FAULT DETECTION

VP1

VX4

MONITORING FAULT

DETECTOR

MASK

SENSE

1-BIT FAULT

DETECTOR

FAULT

WARNINGS

MASK

1-BIT FAULT

DETECTOR

FAULT

MASK

SENSE

1-BIT FAULT

DETECTOR

FAULT

Figure 28. Monitoring Fault Detector Block Diagram

TIMEOUT DETECTOR

The timeout detector allows the user to trap a failure to make

proper progress through a power-up or power-down sequence.

In the sample application shown in Figure 26, the timeout next-

state transition is from the EN3V3 and EN2V5 states. For the

EN3V3 state, the signal 3V3ON is asserted upon entry to this

state (on the PDO1 output pin) to turn on a 3.3 V supply. This

supply rail is connected to the VP2 pin, and the sequence detec-

tor looks for the VP2 pin to go above its UV threshold, which is

set in the supply fault detector (SFD) attached to that pin.

The power-up sequence progresses when this change is

detected. If, however, the supply fails (perhaps due to a short

circuit overloading this supply), then the timeout block traps

the problem. In this example, if the 3.3 V supply fails within

10 ms, then the SE moves to the DIS3V3 state and turns off this

supply by bringing PDO1 low. It also indicates that a fault has

occurred by taking PDO3 high. Timeout delays of from 100 μs

to 400 ms can be programmed.

FAULT REPORTING

The ADM1069 has a fault latch for recording faults. Two registers

are set aside for this purpose. A single bit is assigned to each

input of the device, and a fault on that input sets the relevant bit.

The contents of the fault register can be read out over the

SMBus to determine which input(s) faulted. The fault register

can be enabled/disabled in each state. This ensures that only real

faults are captured and not, for example, undervoltage trips

when the SE is executing a power-down sequence.

相关PDF资料 |

PDF描述 |

|---|---|

| ADM1069ACP-REEL | SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| ADM1069ACP-REEL7 | SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| ADM1070 | -48 V Hot Swap Controller |

| ADM1070ART | -48 V Hot Swap Controller |

| ADM1072ARQ | Dual, USB 2.0 Full/Standby Power Controller with Supply Steering |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADM1069ACP-REEL | 制造商:AD 制造商全称:Analog Devices 功能描述:SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| ADM1069ACP-REEL7 | 制造商:AD 制造商全称:Analog Devices 功能描述:SUPER SEQUENCER-TM WITH MARGINING CONTROL AND AUXILIARY ADC INPUTS |

| ADM1069ACPZ | 功能描述:IC SUPERVISOR/SEQ PROG 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:Super Sequencer® 其它有关文件:STM6717 View All Specifications 标准包装:1 系列:- 类型:多压监控器 监视电压数目:2 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:1.11V,3.075V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:Digi-Reel® 产品目录页面:1194 (CN2011-ZH PDF) 其它名称:497-7019-6 |

| ADM1069ACPZ-REEL | 功能描述:IC SUPERVISOR/SEQ PROG 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:Super Sequencer® 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:高有效 复位超时:- 电压 - 阀值:1.8V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:6-TSOP(0.059",1.50mm 宽)5 引线 供应商设备封装:5-TSOP 包装:剪切带 (CT) 其它名称:NCP301HSN18T1GOSCT |

| ADM1069ACPZ-REEL7 | 功能描述:IC SUPERVISOR/SEQ PROG 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:Super Sequencer® 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:高有效 复位超时:- 电压 - 阀值:1.8V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:6-TSOP(0.059",1.50mm 宽)5 引线 供应商设备封装:5-TSOP 包装:剪切带 (CT) 其它名称:NCP301HSN18T1GOSCT |

发布紧急采购,3分钟左右您将得到回复。