- 您现在的位置:买卖IC网 > PDF目录1777 > ADP3207CJCPZ-RL (ON Semiconductor)IC CTLR SYNC BUCK 7BIT 40-LFCSP PDF资料下载

参数资料

| 型号: | ADP3207CJCPZ-RL |

| 厂商: | ON Semiconductor |

| 文件页数: | 17/32页 |

| 文件大小: | 0K |

| 描述: | IC CTLR SYNC BUCK 7BIT 40-LFCSP |

| 标准包装: | 2,500 |

| 应用: | 控制器,Intel IMVP-6 |

| 输入电压: | 3.3 V ~ 22 V |

| 输出数: | 3 |

| 输出电压: | 0.3 V ~ 1.5 V |

| 工作温度: | -10°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

�� �

�

ADP3207C�

�code� to� an� analog� reference� voltage.� During� startup,� the� DAC�

�ignores� the� VID� code.� The� internal� DAC� steps� through� each�

�VID� code� from� 0� V� to� the� boot� voltage.� The� DAC� steps� to� the�

�next� VID� code� every� 16� m� s.� With� 12.5� mV� difference� between�

�VID� codes,� the� soft� ?� start� slew� rate� is� 12.5� mV� /� 16� m� s� or�

�approximately� 0.78� mV/� m� s.� This� gives� a� soft� ?� start� time� of�

�approximately� 1.5� ms.�

�After� the� DAC� reaches� the� boot� voltage,� an� internal� 100� m� s�

�timer� starts.� This� is� the� 100� m� s� boot� time.� After� the� boot� time�

�is� over,� the� CLKEN� is� asserted� low.� The� DAC� then� reads� the�

�VID� code.� There� is� a� soft� transition� from� the� boot� voltage� to�

�the� VID� voltage.� After� CLKEN� is� asserted� low,� these� is� an�

�decrease� the� acoustic� noise� generated� by� the� MLCC� input�

�capacitors� and� inductors.�

�The� soft� transient� feature� is� implemented� internally.� When�

�the� ADP3207C� detects� a� new� VID� code,� the� DAC� steps�

�through� each� VID� code� until� is� reaches� the� final� code.� For� a�

�fast� slew� rate,� the� ADP3207C� steps� to� the� next� VID� code�

�every� 1� m� s.� This� gives� a� fast� slew� rate� of� 12.5� mV/� m� s.� For� a�

�slow� slew� rate,� the� ADP3207C� steps� to� the� next� VID� code�

�every� 4� m� s.� This� gives� a� slew� rate� of� 3.125� mV� /� m� s.�

�With� DPRSLP� asserted� high,� the� slow� slew� rate� is� enabled.�

�With� DPRSLP� asserted� low,� the� fast� slew� rate� is� enabled.�

�Table� 2� summarizes� the� soft� transient� slew� rate.�

�internal� 8� ms� timer� that� asserts� PWRGD� high.� The� whole�

�powerup� sequence,� including� soft� ?� start,� is� illustrated� in�

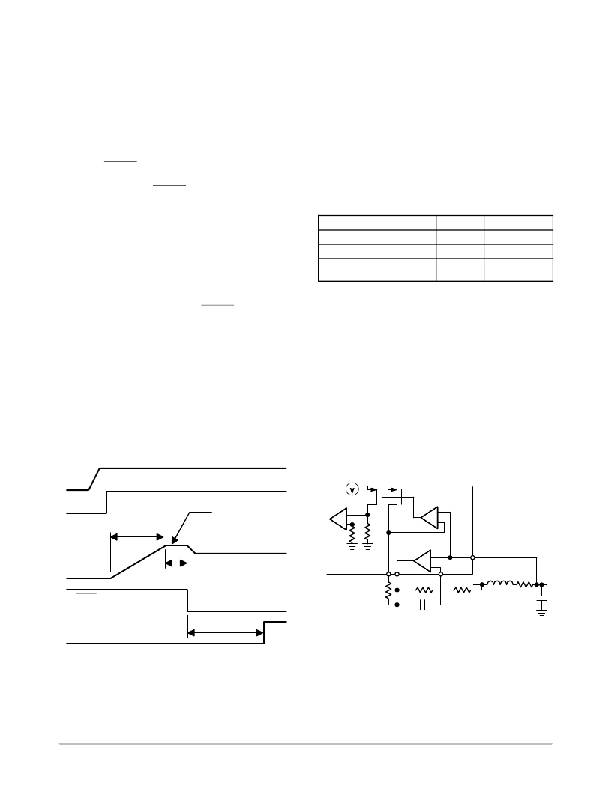

�Figure� 26.�

�Table� 2.� Soft� Transient� Slew� Rate�

�VID� Transient� DPRSLP�

�Slew� Rate�

�In� V� CC� UVLO� or� in� shutdown,� PWM1,� PWM2,� and�

�PWM3� are� pulled� low.� When� V� CC� ramps� above� the� upper�

�UVLO� threshold� and� EN� is� asserted� high,� the� ADP3207C�

�enables� internal� bias� and� starts� a� reset� cycle� that� lasts� about�

�Fast� Exit� from� Deeper� Sleep�

�Slow� Exit� from� Deeper� Sleep�

�Transient� from� V� BOOT� to� VID�

�LOW�

�HIGH�

�DNC�

�(Note� 1)�

�+12.5� mV/� m� s�

�+3.125� mV/� m� s�

�$� 3.125� mV/� m� s�

�50� m� s� to� 60� m� s.� Next,� when� initial� reset� is� over,� the� chip� detects�

�the� number� of� phases� set� by� the� user� and� gives� a� go� signal� to�

�start� the� internal� soft� ?� start.� After� the� CLKEN� is� asserted� low,�

�the� ADP3207C� reads� the� VID� codes� provided� by� the� CPU� on�

�VID0� to� VID6� input� pins.� The� VCore� voltage� changes� from�

�V� BOOT� to� the� VID� voltage� by� a� well� ?� controlled� soft�

�transition,� as� introduced� in� the� Soft� Transient� section.�

�The� PWRGD� signal� is� not� asserted� until� there� is� a�

�t� CPU_PWRGD� delay� of� approximately� 8� ms,� which� is� fixed�

�internally� by� the� ADP3207C.�

�If� either� EN� is� taken� low� or� V� CC� drops� below� the� lower� V� CC�

�UVLO� threshold,� the� PWM1,� PWM2,� and� PWM3� signals�

�stop� switching.� An� internal� MOSFET� discharges� the� output�

�voltage� through� the� CSREF� pin.� The� internal� CSREF�

�MOSFET� has� a� resistance� of� approximately� 100� W� .�

�V5_S�

�1.� DNC� =� Do� Not� Care.�

�Current� Limit�

�The� ADP3207C� compares� the� differential� output� of� a�

�current� sense� amplifier� to� a� programmable� current� limit�

�setpoint� to� provide� current� limiting� function.� The� current� limit�

�set� point� is� set� with� a� resistor� connected� from� I� LIM� pin� to�

�CSCOMP� pin.� This� is� the� R� lim� resistor.� During� normal�

�operation,� the� voltage� on� the� ILIM� pin� is� equal� to� the� CSREF�

�pin.� The� voltage� across� R� lim� is� equal� to� the� voltage� across� the�

�current� sense� amplifier� (from� CSREF� pin� to� CSCOMP� pin).�

�This� voltage� is� proportional� to� output� current.� The� current�

�through� R� lim� is� proportional� to� the� output� inductor� current.�

�The� current� through� R� lim� is� compared� with� an� internal�

�reference� current.� When� the� R� lim� current� goes� above� the�

�internal� reference� current,� the� ADP3207C� goes� into� current�

�limit.� The� current� limit� circuit� is� shown� in� Figure� 11.�

�20� m� A�

�EN�

�V� BOOT�

�CLA�

�?�

�I� LIM�

�I� LIM�

�VI� CONV�

�+�

�Soft� ?� Start�

�t�

�+�

�?�

�V� HID�

�CSA�

�+�

�CSREF�

�VCore�

�t� Boot�

�ILIM�

�?�

�CSCOMP�

�CSSUM�

�L�

�DCR�

�CLKEN�

�R� CS�

�C� CS�

�R� PH�

�C� BULK�

�t� PWRGD� Delay�

�PWRGD�

�Figure� 26.� Powerup� Sequence�

�Soft� Transient�

�The� ADP3207C� provides� a� soft� transient� function� to�

�reduce� inrush� current� during� various� transitions,� including�

�the� entrance/exit� of� deeper� sleep� and� the� transition� from�

�V� BOOT� to� VID� voltage.� Reducing� the� inrush� current� helps�

�Figure� 27.� Current� Limit� Circuit�

�During� startup� when� the� output� voltage� is� below� 200� mV,� a�

�secondary� current� limit� is� activated.� This� is� necessary� because�

�the� voltage� swing� on� CSCOMP� cannot� extend� below� ground.�

�The� secondary� current� limit� circuit� clamps� the� internal� COMP�

�voltage� and� sets� the� internal� compensation� ramp� termination�

�voltage� at� 1.5� V� level.� The� clamp� actually� limits� voltage� drop�

�across� the� low� side� MOSFETs� through� the� current� balance�

�circuitry.�

�http://onsemi.com�

�17�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADP3207DJCPZ-RL | IC CTLR BUCK 7BIT MULTI 40LFCSP |

| ADP3208CJCPZ-RL | IC CTLR BUCK 7BIT IMVP6 48LFCSP |

| ADP3208DJCPZ-RL | IC CTLR BUCK 7BIT 2PHASE 48LFCSP |

| ADP320ACPZ-110-R7 | IC REG LDO 3.3/3.3/1.5V 16LFCSP |

| ADP3210MNR2G | IC CTLR BUCK 7BIT MULTIPH 40QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP3207D | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:7-Bit Programmable, Multi-Phase Mobile, CPU Synchronous Buck |

| ADP3207DJCPZ-RL | 功能描述:DC/DC 开关控制器 IMVP6 BUCK CONTROLLER RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| ADP3207JCPZ-RL | 功能描述:DC/DC 开关控制器 IMVP6 MLTI/PHSE CNTR RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| ADP3208AJCPZ-RL | 功能描述:肖特基二极管与整流器 IMVP6 MLT-PH CTRL W/DRVR RoHS:否 制造商:Skyworks Solutions, Inc. 产品:Schottky Diodes 峰值反向电压:2 V 正向连续电流:50 mA 最大浪涌电流: 配置:Crossover Quad 恢复时间: 正向电压下降:370 mV 最大反向漏泄电流: 最大功率耗散:75 mW 工作温度范围:- 65 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:SOT-143 封装:Reel |

| ADP3208C | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:7-Bit,Programmable,Dual- Phase,Mobile,CPU,Synchronous Buck Controller |

发布紧急采购,3分钟左右您将得到回复。