- 您现在的位置:买卖IC网 > PDF目录17040 > ADS1259EVM (Texas Instruments)EVAL MODULE FOR ADS1259 PDF资料下载

参数资料

| 型号: | ADS1259EVM |

| 厂商: | Texas Instruments |

| 文件页数: | 15/48页 |

| 文件大小: | 0K |

| 描述: | EVAL MODULE FOR ADS1259 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 14k |

| 数据接口: | 串行,SPI? |

| 工作温度: | -40°C ~ 125°C |

| 已用 IC / 零件: | ADS1259 |

| 已供物品: | 板 |

| 其它名称: | 296-29312 ADS1259EVM-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

SCLK

RESETPWDN

/

t

LOW

t

RHSC

CLK

DVDD

InternalReset

1Vnom

AVDD

AVSS

-

3.5Vnom

2

16

t

CLK

ADS1259Operational

SBAS424D

– JUNE 2009 – REVISED AUGUST 2011

RESET/PWDN

RESET

The RESET/PWDN pin has two functions: device

There are three methods to reset the ADS1259: cycle

power-down and device reset. Momentarily holding

the power supplies, take RESET/PWDN low, or send

the pin low resets the device and holding the pin low

the RESET opcode command.

for 216 fCLK cycles activates the Power-Down mode.

When using the RESET/PWDN pin, take it low to

force a reset. Make sure to follow the minimum pulse

POWER-DOWN MODE

width timing specifications before taking the RESET

pin back high.

In power-down mode, internal circuit blocks are

disabled (including the oscillator, reference, and SPI)

The RESET command takes effect on the eighth

and the device enters a micro-power state. To

falling SCLK edge of the opcode command. On reset,

engage power-down mode, hold the RESET/PWDN

the configuration registers are initialized to the default

pin low for 216 fCLK cycles. Note that the register

states and the conversion cycle restarts. After reset,

contents are not saved because they are reset when

allow eight fCLK cycles before communicating to the

RESET/PWDN goes high.

ADS1259. Note that when using the reset command,

the SPI interface itself may require reset before

Keep the digital inputs at defined VIH or VINL logic

accepting

the

command.

See

the

levels (do not 3-state). To minimize power-supply

Characteristics section for details.

leakage current, disable the external clock. Note that

the

ADS1259

digital

outputs

remain

active

in

power-down. The analog signal inputs may float.

POWER-ON SEQUENCE

To exit power-down, take RESET/PWDN high. Wait

The ADS1259 has three power supplies: AVDD,

216

fCLK

cycles

before

communicating

to

the

AVSS, and DVDD. The supplies can be sequenced in

ADS1259, as shown in Figure 48.

any order but be sure that at any time the analog

inputs do not exceed AVDD or AVSS and the digital

inputs do not exceed DVDD. After the last power

supply

has

crossed

the

respective

power-on

threshold,

216

fCLK cycles are counted before

releasing the internal reset. After the internal reset is

released, the ADS1259 is ready for operation.

Figure 49 shows the power-on sequence of the

ADS1259.

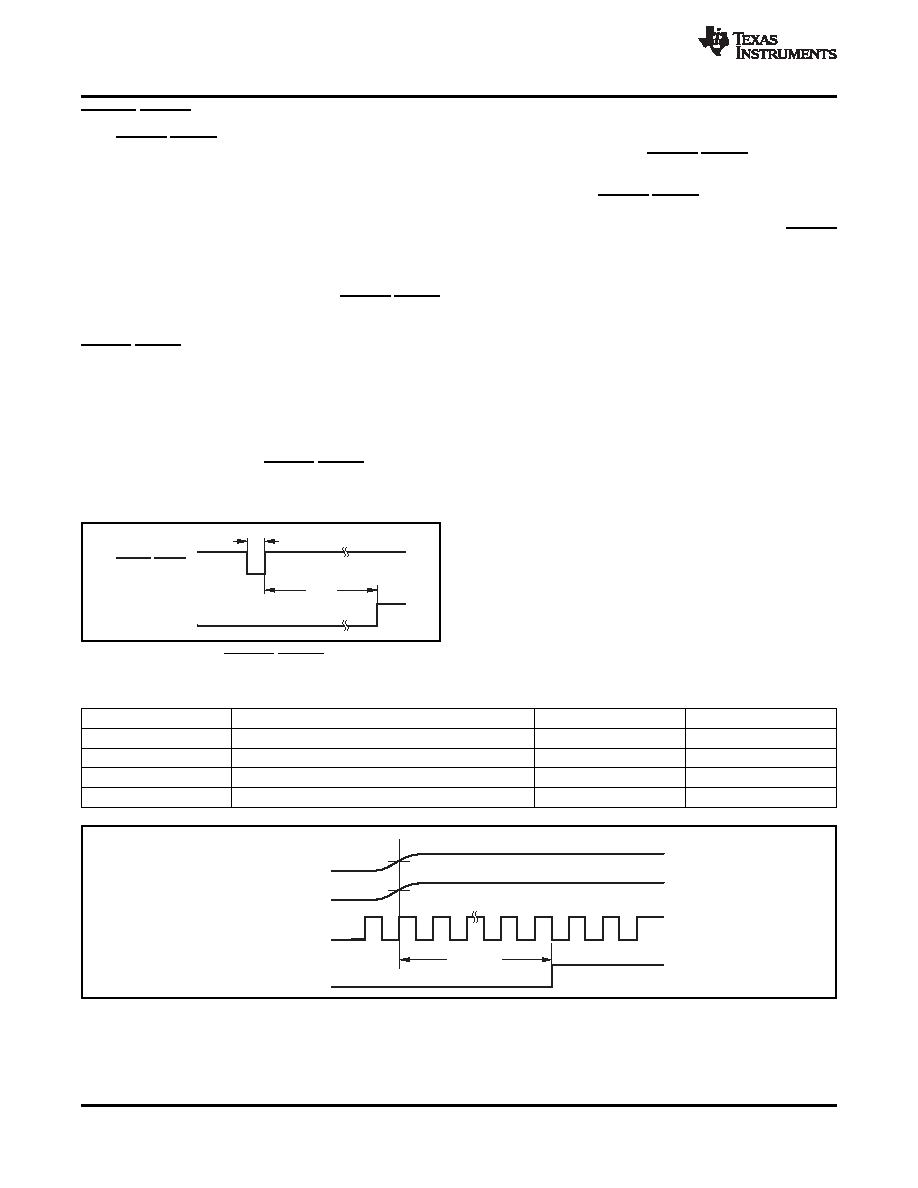

Figure 48. RESET/PWDN Timing

Table 6. Timing Characteristics for Figure 48

SYMBOL

DESCRIPTION

MIN

UNIT

tLOW

Pulse width low for reset

4

tCLK

tLOW

Pulse width low for power-down

216

tCLK

tRHSC

Reset high to SPI communication start

8

tCLK

tRHSC

Exit power-down to SPI communication start

216

tCLK

Figure 49. Power-On Sequence

22

Copyright

2009–2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| 0210490281 | CABLE JUMPER 1.25MM .076M 22POS |

| EBC19DREN-S93 | CONN EDGECARD 38POS .100 EYELET |

| EEC19DRYN-S93 | CONN EDGECARD 38POS DIP .100 SLD |

| EBC19DREH-S93 | CONN EDGECARD 38POS .100 EYELET |

| MLK1005S2N4S | INDUCTOR MULTILAYER 2.4NH 0402 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS1259EVM | 制造商:Texas Instruments 功能描述:DEVELOPMENT TOOL |

| ADS1259EVM-PDK | 功能描述:数据转换 IC 开发工具 ADS1259 Perf Demo Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| ADS1259EVM-PDK | 制造商:Texas Instruments 功能描述:DEVELOPMENT TOOL |

| ADS1259IPW | 功能描述:模数转换器 - ADC Low-Noise 14kSPS 24B ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS1259IPW | 制造商:Texas Instruments 功能描述:A/D CONVERTER (A-D) IC |

发布紧急采购,3分钟左右您将得到回复。