- 您现在的位置:买卖IC网 > PDF目录1899 > ADSP-21371BSWZ-2B (Analog Devices Inc)IC DSP 32BIT 266MHZ 208-LQFP PDF资料下载

参数资料

| 型号: | ADSP-21371BSWZ-2B |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 266MHZ 208-LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI |

| 时钟速率: | 266MHz |

| 非易失内存: | ROM(512 kB) |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-LQFP 裸露焊盘 |

| 供应商设备封装: | 208-LQFP-EP(28x28) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

ADSP-21371

S/PDIF Transmitter

Serial data input to the S/PDIF transmitter can be formatted as

left justified, I2S, or right justified with word widths of 16-, 18-,

20-, or 24-bits. The following sections provide timing for the

transmitter.

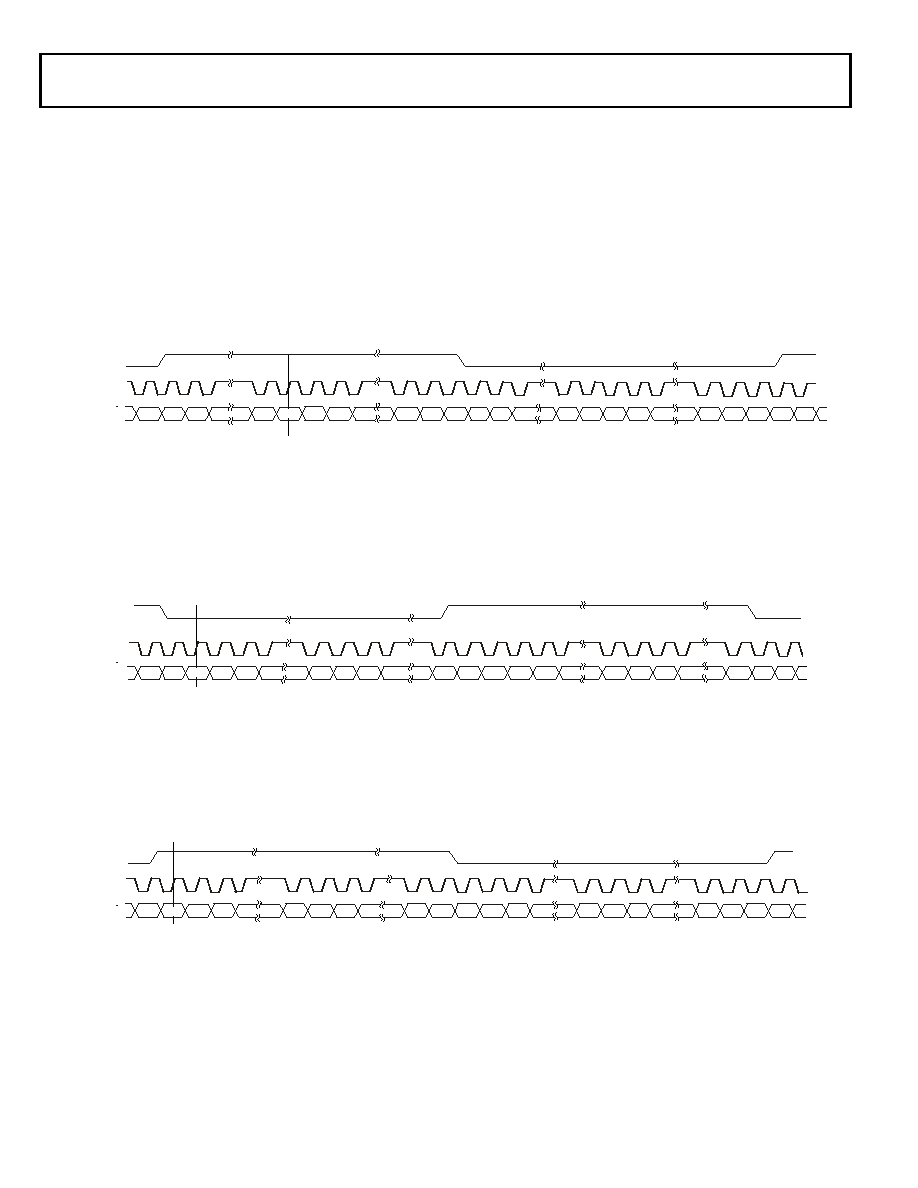

S/PDIF Transmitter-Serial Input Waveforms

Figure 24 shows the right-justified mode. LRCLK is high for the

left channel and low for the right channel. Data is valid on the

rising edge of SCLK. The MSB is delayed 12-bit clock periods

(in 20-bit output mode) or 16-bit clock periods (in 16-bit output

DAI_P20-1

LRCLK

DAI_P20-1

SCLK

DAI_P20-1

SDATA

mode) from an LRCLK transition, so that when there are 64

SCLK periods per LRCLK period, the LSB of the data will be

right-justified to the next LRCLK transition.

LEFT CHANNEL

RIGHT CHANNEL

MS B-1

MSB-2

LSB+2 LSB+1

LSB

MSB

MSB-1

MSB-2

LS B+2

LSB+1

LSB

MSB

Figure 24. Right-Justified Mode

for the left channel and HI for the right channel. Data is valid on

the rising edge of SCLK. The MSB is left-justified to an LRCLK

transition but with a single SCLK period delay.

DAI_P20-1

LRCLK

DAI_P20-1

SCLK

DAI_P20-1

SDATA

MSB-1

MS B-2

LS B+2

LSB+1

LSB

LEFT CHANNEL

MSB

MS B-1

MS B-2

LSB+2

LS B+1

LSB

MSB

RIGHT CHANNEL

Figure 25. I2S-Justified Mode

Figure 26 shows the left-justified mode. LRCLK is high for the

left channel and LO for the right channel. Data is valid on the

rising edge of SCLK. The MSB is left-justified to an LRCLK

transition with no MSB delay.

DAI_P20-1

LRCLK

DAI_P20-1

SCLK

DAI_P20-1

SDATA

LEFT CHANNEL

RIGHT CHANNEL

MSB-1

MSB-2

LS B+2

L SB+1

LSB

MSB

MSB-1

MSB-2

LSB+2

LSB +1

L SB

MSB

MSB+1

MSB

Figure 26. Left-Justified Mode

Rev. 0

|

Page 36 of 48

|

June 2007

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-21469BBCZ-3 | IC DSP 32/40BIT 400MHZ 324BGA |

| ADSP-21479BBCZ-2A | IC DSP SHARC 266MHZ LP 196CSPBGA |

| ADSP-21479KBCZ-3A | IC DSP SHARK 300MHZ 196CSPBGA |

| ADSP-21489BSWZ-3B | IC CCD SIGNAL PROCESSOR 176LQFP |

| ADSP-2171BSTZ-133 | IC DSP CONTROLLER 16BIT 128TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21371BSWZ-2B2 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor optimized for high performance audio processing |

| ADSP-21371KSWZ-2A | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit/40-Bit 266MHz 266MIPS 208-Pin LQFP EP 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT/40-BIT 266MHZ 266MIPS 208LQFP EP - Trays 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-21371KSWZ-2A2 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor optimized for high performance audio processing |

| ADSP-21371KSWZ-2B | 功能描述:IC DSP 32BIT 266MHZ 208-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21371KSWZ-2B2 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor optimized for high performance audio processing |

发布紧急采购,3分钟左右您将得到回复。