- 您现在的位置:买卖IC网 > PDF目录1899 > ADSP-21469BBCZ-3 (Analog Devices Inc)IC DSP 32/40BIT 400MHZ 324BGA PDF资料下载

参数资料

| 型号: | ADSP-21469BBCZ-3 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/72页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32/40BIT 400MHZ 324BGA |

| 产品变化通告: | Pin Function Change 08/Mar/2012 |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI,EBI/EMI,I²C,SCI,SPI,SSP,UART/USART |

| 时钟速率: | 400MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 5Mb |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.05V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 324-BGA,CSPBGA |

| 供应商设备封装: | 324-CSPBGA |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

Rev. 0

|

Page 24 of 72

|

June 2010

ADSP-21469

Clock Input

Clock Signals

The ADSP-21469 can use an external clock or a crystal. See the

CLKIN pin description in Table 9. Programs can configure the

processor to use its internal clock generator by connecting the

necessary components to CLKIN and XTAL. Figure 8 shows the

component connections used for a crystal operating in funda-

mental mode. Note that the clock rate is achieved using a

25 MHz crystal and a PLL multiplier ratio 16:1 (CCLK:CLKIN

achieves a clock speed of 400 MHz).

To achieve the full core clock rate, programs need to configure

the multiplier bits in the PMCTL register.

Table 18. Clock Input

Parameter

400 MHz1

1 Applies to all 400 MHz models. See Ordering Guide on Page 70.

450 MHz2

2 Applies to all 450 MHz models. See Ordering Guide on Page 70.

Unit

Min

Max

Min

Max

Timing Requirements

tCK

CLKIN Period

153

3 Applies only for CLK_CFG1–0 = 00 and default values for PLL control bits in PMCTL.

100

13.26

100

ns

tCKL

CLKIN Width Low

7.5

45

6.63

45

ns

tCKH

CLKIN Width High

7.5

45

6.63

45

ns

tCKRF

CLKIN Rise/Fall (0.4 V to 2.0 V)

34

4 Guaranteed by simulation but not tested on silicon.

ns

tCCLK

5

5 Any changes to PLL control bits in the PMCTL register must meet core clock timing specification t

CCLK.

CCLK Period

2.5

10

2.22

10

ns

fVCO

6

6 See Figure 5 on Page 22 for VCO diagram.

VCO Frequency

200

900

200

900

MHz

tCKJ

7, 8

7 Actual input jitter should be combined with ac specifications for accurate timing analysis.

8 Jitter specification is maximum peak-to-peak time interval error (TIE) jitter.

CLKIN Jitter Tolerance

–250

+250

–250

+250

ps

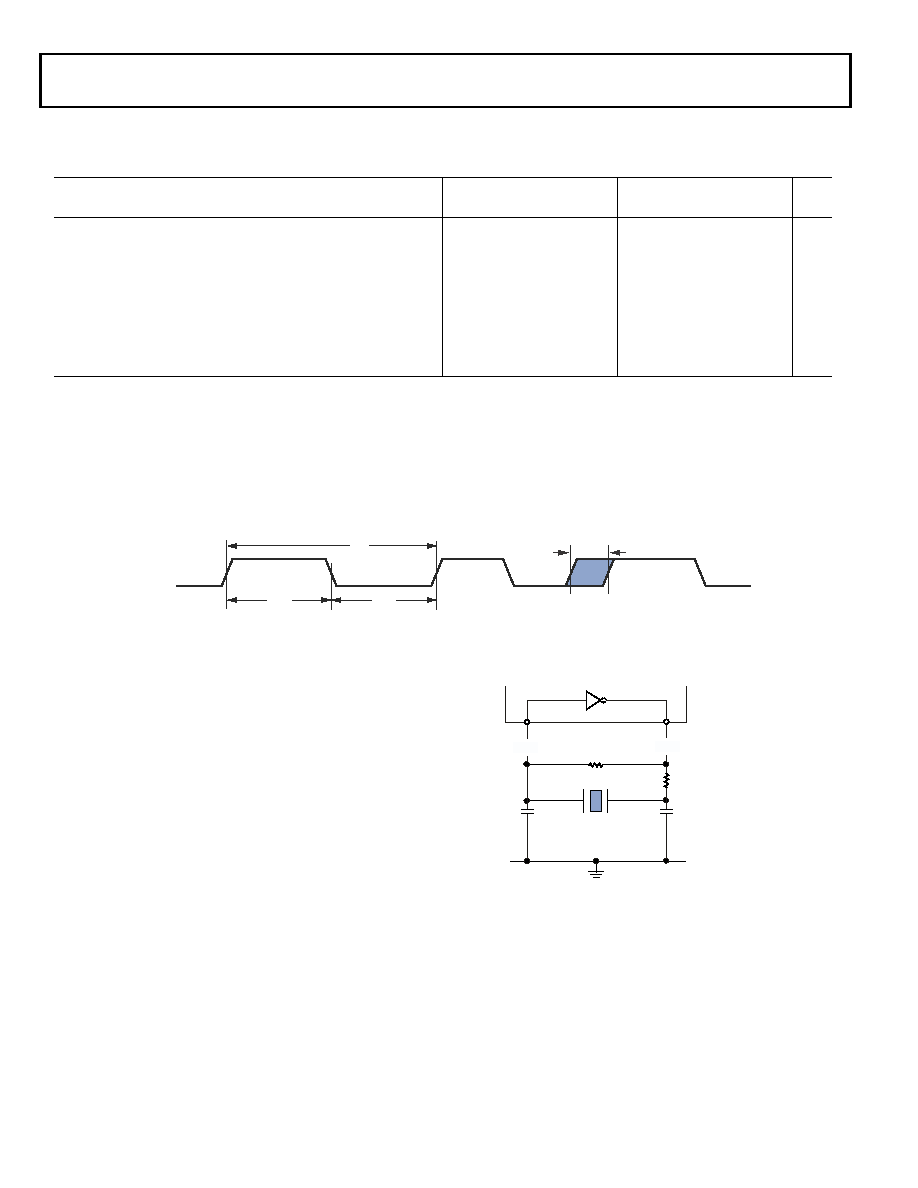

Figure 7. Clock Input

CLKIN

tCK

tCKL

tCKH

tCKJ

Figure 8. Recommended Circuit for

Fundamental Mode Crystal Operation

C1

22pF

Y1

R1

1M

: *

XTAL

CLKIN

C2

22pF

25.000 MHz

R2

47

:*

R2 SHOULD BE CHOSEN TO LIMIT CRYSTAL

DRIVE POWER. REFER TO CRYSTAL

MANUFACTURER’S SPECIFICATIONS

*TYPICAL VALUES

ADSP-2146x

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-21479BBCZ-2A | IC DSP SHARC 266MHZ LP 196CSPBGA |

| ADSP-21479KBCZ-3A | IC DSP SHARK 300MHZ 196CSPBGA |

| ADSP-21489BSWZ-3B | IC CCD SIGNAL PROCESSOR 176LQFP |

| ADSP-2171BSTZ-133 | IC DSP CONTROLLER 16BIT 128TQFP |

| ADSP-2181KSZ-160 | IC DSP CONTROLLER 16BIT 128-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21469KBCZ-3 | 功能描述:IC DSP 32/40BIT 400MHZ 324BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21469KBCZ-4 | 功能描述:IC DSP 32/40BIT 450MHZ 324BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP21469KBCZENG | 制造商:Analog Devices 功能描述: |

| ADSP-21469KBCZ-ENG | 制造商:Analog Devices 功能描述:FXD PT PROC - Trays |

| ADSP-21469KBCZ-X | 制造商:Analog Devices 功能描述:FXD PT PROC - Trays |

发布紧急采购,3分钟左右您将得到回复。