- 您现在的位置:买卖IC网 > PDF目录19399 > ADSP-21478KSWZ-1A (Analog Devices Inc)IC DSP SHARC 200MHZ LP 100LQFP PDF资料下载

参数资料

| 型号: | ADSP-21478KSWZ-1A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/72页 |

| 文件大小: | 0K |

| 描述: | IC DSP SHARC 200MHZ LP 100LQFP |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI,EBI/EMI,I²C,SPI,SPORT,UART/USART |

| 时钟速率: | 200MHz |

| 非易失内存: | ROM(4Mb) |

| 芯片上RAM: | 3Mb |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP 裸露焊盘 |

| 供应商设备封装: | 100-LQFP-EP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

Rev. A

|

Page 34 of 72

|

September 2011

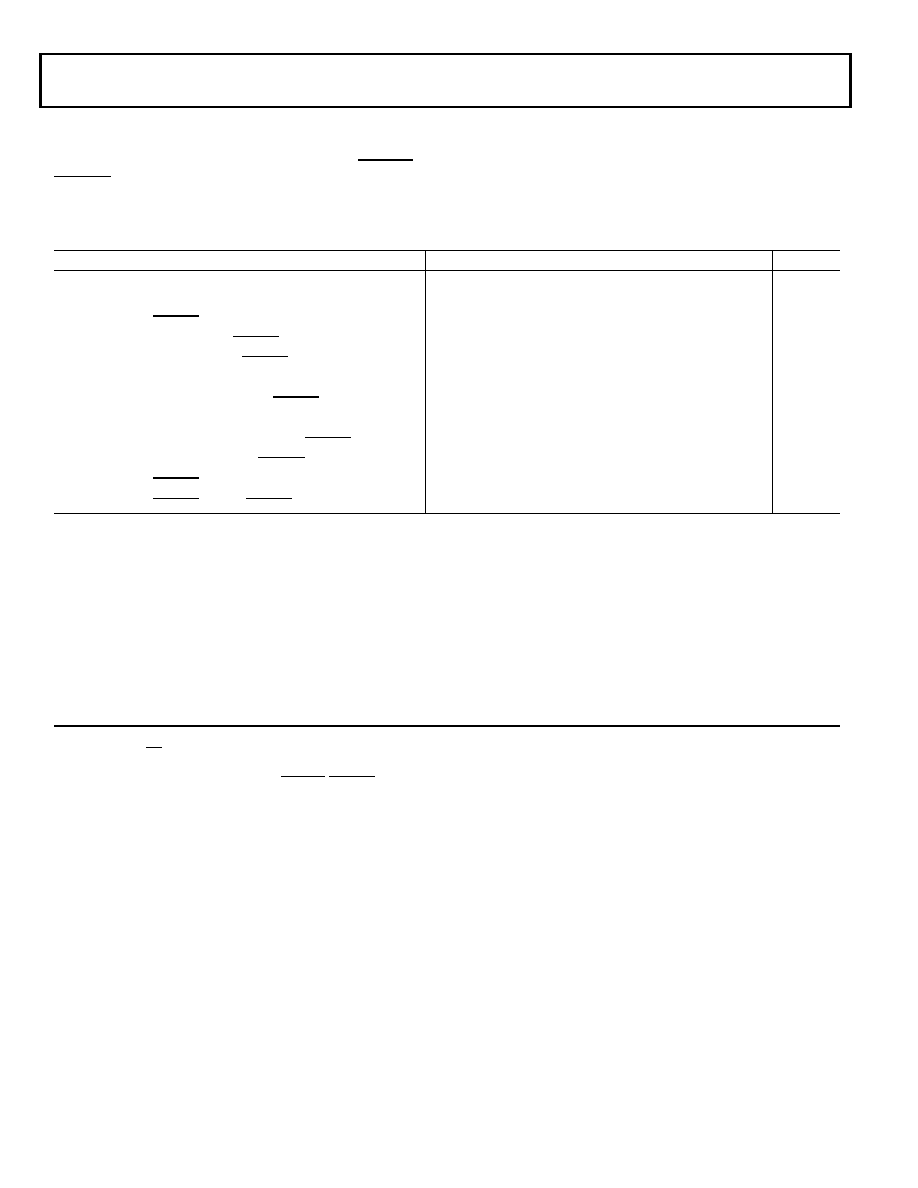

AMI Read

Use these specifications for asynchronous interfacing to memo-

ries. Note that timing for AMI_ACK, ADDR, DATA, AMI_RD,

AMI_WR, and strobe timing parameters only apply to asyn-

chronous access mode.

Table 31. AMI Read

Parameter

Min

Max

Unit

Timing Requirements

tDAD

1, 2, 3

Address Selects Delay to Data Valid

W + tSDCLK – 6.32

ns

tDRLD

AMI_RD Low to Data Valid

W – 3

ns

tSDS

4, 5

Data Setup to AMI_RD High

2.6

ns

tHDRH

Data Hold from AMI_RD High

0.4

ns

tDAAK

2, 6

AMI_ACK Delay from Address Selects

tSDCLK – 10. + W

ns

tDSAK4

AMI_ACK Delay from AMI_RD Low

W – 7.0

ns

Switching Characteristics

tDRHA

Address Selects Hold After AMI_RD High

RHC+ 0.38

ns

tDARL

Address Selects to AMI_RD Low

tSDCLK – 5

ns

tRW

AMI_RD Pulse Width

W – 1.4

ns

tRWR

AMI_RD High to AMI_RD Low

HI + tSDCLK – 1.2

ns

W = (number of wait states specified in AMICTLx register) × tSDCLK.

RHC = (number of Read Hold Cycles specified in AMICTLx register) × tSDCLK

Where PREDIS = 0

HI = RHC: Read to Read from same bank

HI = RHC + IC: Read to Read from different bank

HI = RHC + Max (IC, (4 × tSDCLK)) : Read to Write from same or different bank

Where PREDIS = 1

HI = RHC + Max (IC, (4 × tSDCLK)) : Read to Write from same or different bank

HI = RHC + (3 × tSDCLK): Read to Read from same bank

HI = RHC + Max (IC, (3 × tSDCLK)) : Read to Read from different bank

IC = (number of idle cycles specified in AMICTLx register) × tSDCLK

H = (number of hold cycles specified in AMICTLx register) × tSDCLK.

1 Data delay/setup: System must meet tDAD, tDRLD, or tSDS.

2 The falling edge of MSx, is referenced.

3 The maximum limit of timing requirement values for tDAD and tDRLD parameters are applicable for the case where AMI_ACK is always high.

4 Note that timing for AMI_ACK, ADDR, DATA, AMI_RD, AMI_WR, and strobe timing parameters only apply to asynchronous access mode.

5 Data hold: User must meet t

HDRH in asynchronous access mode. See Test Conditions on Page 61 for the calculation of hold times given capacitive and dc loads.

6 AMI_ACK delay/setup: User must meet tdaak, or tdsak, for deassertion of AMI_ACK (low).

相关PDF资料 |

PDF描述 |

|---|---|

| ACM30DTMH | CONN EDGECARD 60POS R/A .156 SLD |

| VI-J6K-IZ | CONVERTER MOD DC/DC 40V 25W |

| ACM30DTMD | CONN EDGECARD 60POS R/A .156 SLD |

| TAJC335M050RNJ | CAP TANT 3.3UF 50V 20% 2312 |

| RW2-1209D/H2/SMD | CONV DC/DC 2W 9-18VIN +/-09VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21478KSWZ-2A | 功能描述:IC DSP SHARC 266MHZ LP 100LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21478KSWZ-ENG | 制造商:Analog Devices 功能描述:SHARC PROCESSOR - Trays |

| ADSP-21479 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21479BBCZ-2A | 功能描述:IC DSP SHARC 266MHZ LP 196CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21479BBCZ-2AX | 制造商:Analog Devices 功能描述:- Trays |

发布紧急采购,3分钟左右您将得到回复。