- 您现在的位置:买卖IC网 > PDF目录19399 > ADSP-21478KSWZ-1A (Analog Devices Inc)IC DSP SHARC 200MHZ LP 100LQFP PDF资料下载

参数资料

| 型号: | ADSP-21478KSWZ-1A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/72页 |

| 文件大小: | 0K |

| 描述: | IC DSP SHARC 200MHZ LP 100LQFP |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI,EBI/EMI,I²C,SPI,SPORT,UART/USART |

| 时钟速率: | 200MHz |

| 非易失内存: | ROM(4Mb) |

| 芯片上RAM: | 3Mb |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP 裸露焊盘 |

| 供应商设备封装: | 100-LQFP-EP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

Rev. A

|

Page 12 of 72

|

September 2011

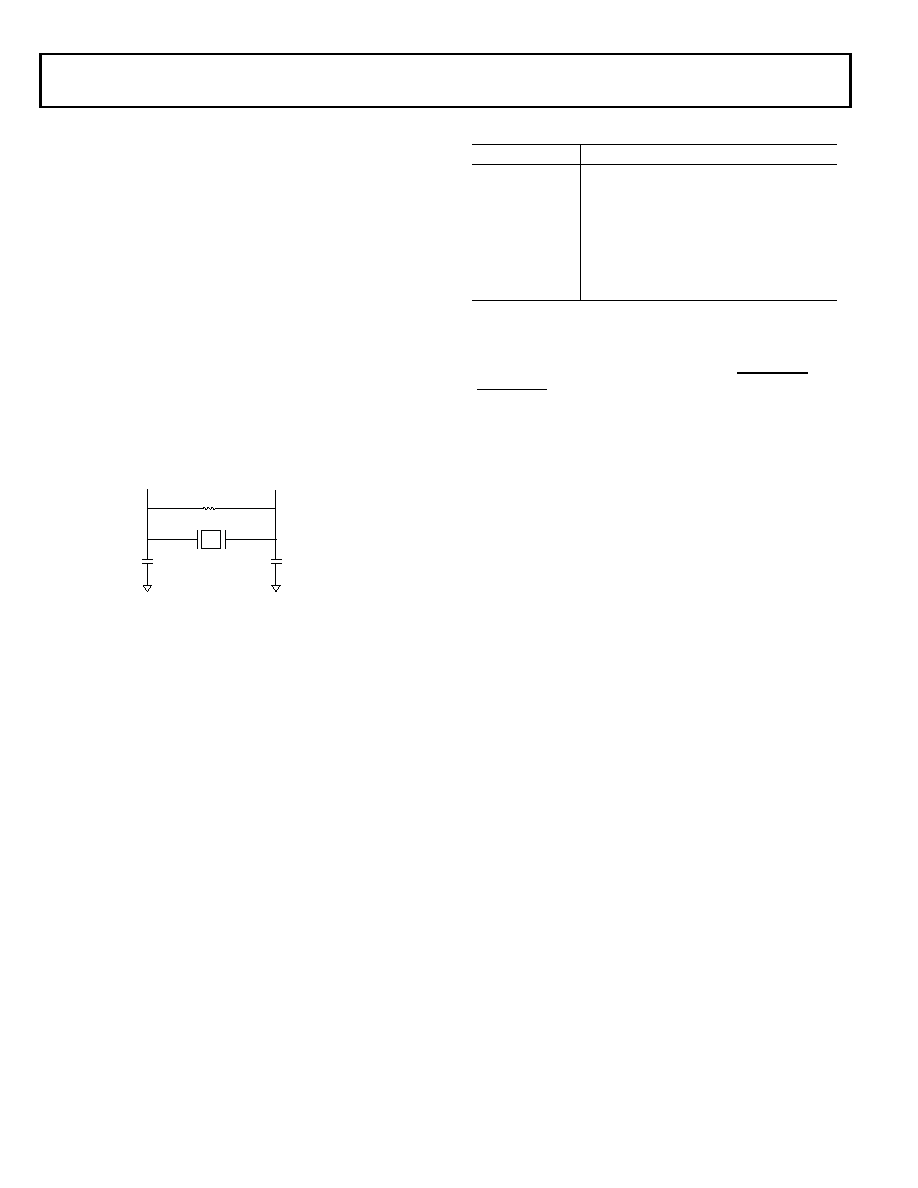

The watch dog timer also has an internal RC oscillator that can

be used as the clock source. The internal RC oscillator can be

used as an optional alternative to using an external clock applied

to the WDT_CLIN pin.

Real-Time Clock

The real-time clock (RTC) provides a robust set of digital watch

features, including current time, stopwatch, and alarm. The

RTC is clocked by a 32.768 kHz crystal external to the SHARC

processor. Connect RTC pins RTXI and RTXO with external

components as shown in Figure 3.

The RTC peripheral has dedicated power supply pins so that it

can remain powered up and clocked even when the rest of the

processor is in a low power state. The RTC provides several pro-

grammable interrupt options, including interrupt per second,

minute, hour, or day clock ticks, interrupt on programmable

stopwatch countdown, or interrupt at a programmed alarm

time. An RTCLKOUT signal that operates at 1 Hz is also pro-

vided for calibration.

The 32.768 kHz input clock frequency is divided down to a 1 Hz

signal by a prescaler. The counter function of the timer consists

of four counters: a 60-second counter, a 60-minute counter, a

24-hour counter, and an 32,768-day counter. When the alarm

interrupt is enabled, the alarm function generates an interrupt

when the output of the timer matches the programmed value in

the alarm control register. There are two alarms: The first alarm

is for a time of day. The second alarm is for a day and time of

that day.

The stopwatch function counts down from a programmed

value, with one-second resolution. When the stopwatch inter-

rupt is enabled and the counter underflows, an interrupt is

generated.

SYSTEM DESIGN

The following sections provide an introduction to system design

options and power supply issues.

Program Booting

The internal memory boots at system power-up from an 8-bit

EPROM via the external port, an SPI master, or an SPI slave.

Booting is determined by the boot configuration

(BOOT_CFG2–0) pins in Table 9.

A running reset feature is used to reset the processor core and

peripherals without resetting the PLL and SDRAM controller,

or performing a boot. The functionality of the RESETOUT

/RUNRSTIN pin has now been extended to also act as the input

for initiating a running reset. For more information, see the

ADSP-214xx SHARC Processor Hardware Reference.

Power Supplies

The processors have separate power supply connections for the

internal (VDD_INT) and external (VDD_EXT), power supplies. The

internal and analog supplies must meet the VDD_INT specifica-

tions. The external supply must meet the VDD_EXT specification.

All external supply pins must be connected to the same power

supply.

To reduce noise coupling, the PCB should use a parallel pair of

power and ground planes for VDD_INT and GND.

Target Board JTAG Emulator Connector

Analog Devices DSP Tools product line of JTAG emulators uses

the IEEE 1149.1 JTAG test access port of the processors to mon-

itor and control the target board processor during emulation.

Analog Devices DSP Tools product line of JTAG emulators pro-

vides emulation at full processor speed, allowing inspection and

modification of memory, registers, and processor stacks. The

processor's JTAG interface ensures that the emulator will not

affect target system loading or timing.

For complete information on Analog Devices’ SHARC DSP

Tools product line of JTAG emulator operation, see the appro-

priate emulator hardware user’s guide.

DEVELOPMENT TOOLS

The processors are supported with a complete set of CROSS-

CORE

software and hardware development tools, including

Analog Devices emulators and VisualDSP++

development

environment. The same emulator hardware that supports other

SHARC processors also fully emulates the processors.

EZ-KIT Lite Evaluation Board

For evaluation of the processors, use the EZ-KIT Lite

board

being developed by Analog Devices. The board comes with on-

chip emulation capabilities and is equipped to enable software

development. Multiple daughter cards are available.

Figure 3. External Components for RTC

RTXO

C1

C2

X1

NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1.

CONTACT CRYSTAL MANUFACTURER FOR DETAILS. C1 AND C2

SPECIFICATIONS ASSUME BOARD TRACE CAPACITANCE OF 3 pF.

RTXI

R1

Table 9. Boot Mode Selection

BOOT_CFG2–0

1

Booting Mode

000

SPI Slave Boot

001

SPI Master Boot (from Flash and Other Slaves)

010

AMI User Boot (for 8-bit Flash Boot)

011

No Boot (Processor Executes from Internal

ROM After Reset)

100

Reserved

1xx

Reserved

1 The BOOT_CFG2 pin is not available on the 100-lead package.

相关PDF资料 |

PDF描述 |

|---|---|

| ACM30DTMH | CONN EDGECARD 60POS R/A .156 SLD |

| VI-J6K-IZ | CONVERTER MOD DC/DC 40V 25W |

| ACM30DTMD | CONN EDGECARD 60POS R/A .156 SLD |

| TAJC335M050RNJ | CAP TANT 3.3UF 50V 20% 2312 |

| RW2-1209D/H2/SMD | CONV DC/DC 2W 9-18VIN +/-09VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21478KSWZ-2A | 功能描述:IC DSP SHARC 266MHZ LP 100LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21478KSWZ-ENG | 制造商:Analog Devices 功能描述:SHARC PROCESSOR - Trays |

| ADSP-21479 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21479BBCZ-2A | 功能描述:IC DSP SHARC 266MHZ LP 196CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21479BBCZ-2AX | 制造商:Analog Devices 功能描述:- Trays |

发布紧急采购,3分钟左右您将得到回复。