- 您现在的位置:买卖IC网 > PDF目录19388 > ADSP-BF537BBCZ-5B (Analog Devices Inc)IC DSP CTLR 16BIT 208CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF537BBCZ-5B |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/68页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 208CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART |

| 时钟速率: | 500MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.26V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-LFBGA,CSPBGA |

| 供应商设备封装: | 208-CSPBGA |

| 包装: | 托盘 |

| 配用: | ADZS-BF537-ASKIT-ND - BOARD EVAL SKIT ADSP-BF537 ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF537-EZLITE-ND - BOARD EVAL ADSP-BF537 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT ADZS-BF537-STAMP-ND - SYSTEM DEV FOR ADSP-BF537 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. J

|

Page 38 of 68

|

February 2014

Serial Port Timing

through Figure 23 on Page 41 describe serial port operations.

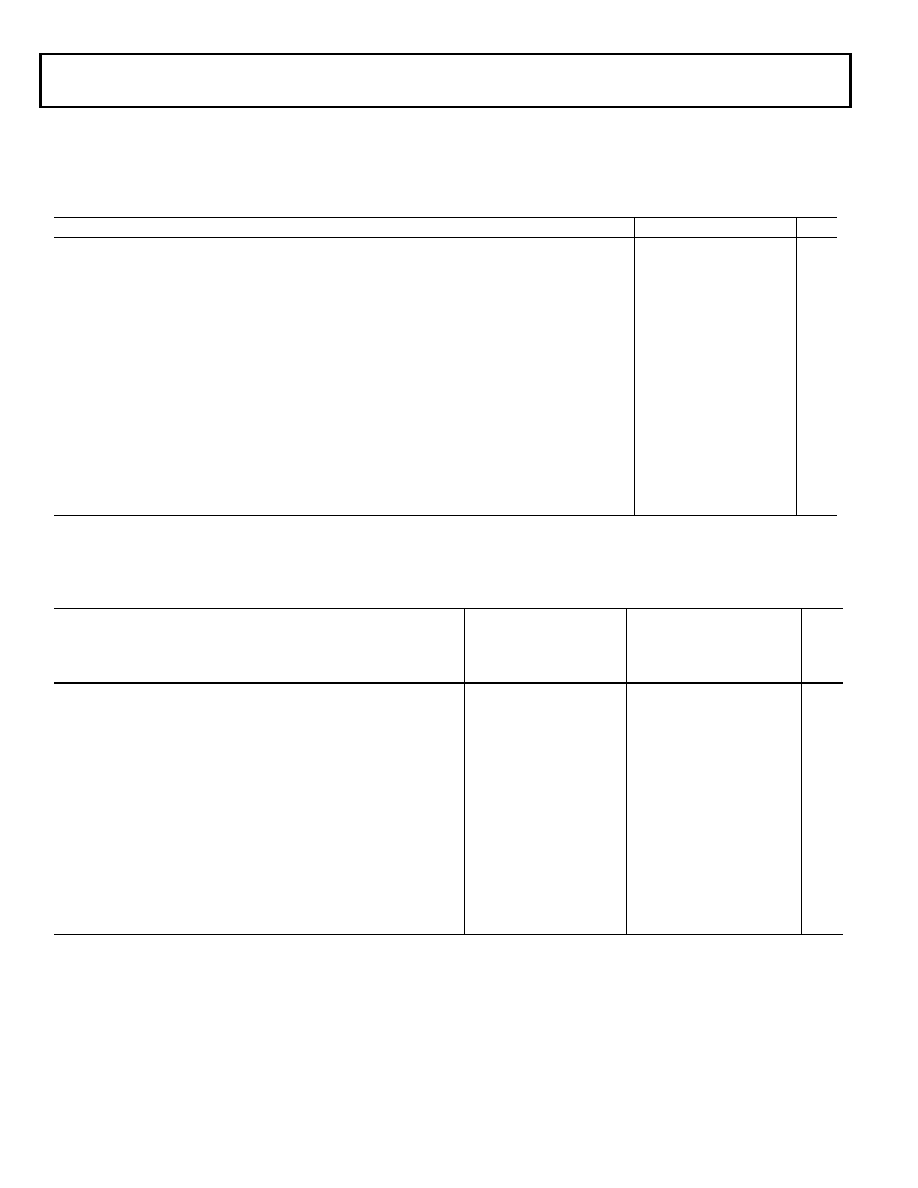

Table 30. Serial Ports—External Clock

Parameter

Min

Max

Unit

Timing Requirements

tSFSE

TFSx/RFSx Setup Before TSCLKx/RSCLKx1

3.0

ns

tHFSE

TFSx/RFSx Hold After TSCLKx/RSCLKx

1

3.0

ns

tSDRE

Receive Data Setup Before RSCLKx

1

3.0

ns

tHDRE

Receive Data Hold After RSCLKx

1

3.0

ns

tSCLKEW

TSCLKx/RSCLKx Width

4.5

ns

tSCLKE

TSCLKx/RSCLKx Period

15.0

ns

tSUDTE

Start-Up Delay From SPORT Enable To First External TFSx2

4.0 × tSCLKE

ns

tSUDRE

Start-Up Delay From SPORT Enable To First External RFSx

4.0 × tSCLKE

ns

Switching Characteristics

tDFSE

TFSx/RFSx Delay After TSCLKx/RSCLK (Internally Generated TFSx/RFSx)

3

10.0

ns

tHOFSE

TFSx/RFSx Hold After TSCLKx/RSCLK (Internally Generated TFSx/RFSx)2

0ns

tDDTE

Transmit Data Delay After TSCLKx2

10.0

ns

tHDTE

Transmit Data Hold After TSCLKx2

0ns

1 Referenced to sample edge.

2 Verified in design but untested. After being enabled, the serial port requires external clock pulses—before the first external frame sync edge—to initialize the serial port.

3 Referenced to drive edge.

Table 31. Serial Ports—Internal Clock

2.25 V

V

DDEXT < 2.70 V

or

0.80 V

V

DDINT < 0.95 V

1

2.70 V

V

DDEXT 3.60 V

and

0.95 V

V

DDINT 1.43 V

2, 3

Parameter

Min

Max

Min

Max

Unit

Timing Requirements

tSFSI

TFSx/RFSx Setup Before TSCLKx/RSCLKx4

8.5

8.0

ns

tHFSI

TFSx/RFSx Hold After TSCLKx/RSCLKx4

–1.5

ns

tSDRI

Receive Data Setup Before RSCLKx

8.5

8.0

ns

tHDRI

Receive Data Hold After RSCLKx

–1.5

ns

Switching Characteristics

tDFSI

TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated

TFSx/RFSx)

5

3.0

ns

tHOFSI

TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated

TFSx/RFSx)

1.0

ns

tDDTI

Transmit Data Delay After TSCLKx

3.0

ns

tHDTI

Transmit Data Hold After TSCLKx

1.0

ns

tSCLKIW

TSCLKx/RSCLKx Width

4.5

ns

1 Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

2 Applies to all nonautomotive-grade devices when operated within these voltage ranges.

3 All automotive-grade devices are within these specifications.

4 Referenced to sample edge.

5 Referenced to drive edge.

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF534YBCZ-4B | IC DSP CTLR 16BIT 400MHZ 208-CSP |

| ADSP-21488BSWZ-3A | IC DSP 3MBIT 400MHZ 100LQFP |

| ADSP-BF544MBBCZ-5M | IC DSP 16BIT 533MHZ MDDR 400CBGA |

| SWS600L-5 | POWER SUPPLY 5V 120A SGL OUTPUT |

| ADSP-BF544BBCZ-5A | IC DSP 16BIT 533MHZ 400CSBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF537BBCZ-5BV | 功能描述:IC DSP CTLR 16BIT 208CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF537BBCZ5BVX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF537BBCZ-5BX | 制造商:Analog Devices 功能描述:208-MEG PB FREE SPARSE - Trays |

| ADSP-BF537KBC-6A | 制造商:Analog Devices 功能描述:DSP FIX PT 16BIT 600MHZ 600MIPS 182CSPBGA - Trays |

| ADSP-BF537KBCZ-6A | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 600MHz 600MIPS 182-Pin CSP-BGA 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

发布紧急采购,3分钟左右您将得到回复。