- 您现在的位置:买卖IC网 > PDF目录10747 > AFE7222IRGCR (Texas Instruments)IC AFE 12BIT 65/130MSPS 64VQFN PDF资料下载

参数资料

| 型号: | AFE7222IRGCR |

| 厂商: | Texas Instruments |

| 文件页数: | 47/106页 |

| 文件大小: | 0K |

| 描述: | IC AFE 12BIT 65/130MSPS 64VQFN |

| 标准包装: | 2,000 |

| 位数: | 12 |

| 通道数: | 4 |

| 功率(瓦特): | 610mW |

| 电压 - 电源,模拟: | 2.85 V ~ 3.6 V |

| 电压 - 电源,数字: | 1.7 V ~ 1.9 V |

| 封装/外壳: | 64-VFQFN 裸露焊盘 |

| 供应商设备封装: | 64-VQFN 裸露焊盘(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

SLOS711B – NOVEMBER 2011 – REVISED MARCH 2012

REG_PDNI_TX : Power downs TX Channel A (I Channel) alone.

REG_PDNQ_TX : Power downs TX Channel B (Q Channel) alone.

REG_PDNI_RX : Power downs RX Channel A (I Channel) alone.

REG_PDNQ_RX : Power downs RX Channel B (Q Channel) alone.

REG_PDN_FRM_REG has a similar role to play for the above modes (REG_PDNI_TX, REG_PDNQ_TX,

REG_PDNI_RX, REG_PDNQ_RX). When REG_PDN_FRM_REG is low, it configures the PDN pin to the

function of the bit that is set. When REG_PDN_FRM_REG is high, the set bit directly controls the

described powerdown mode.

MODE_LP_CMOS : Low power RX CMOS mode. When the RX interface is set to CMOS interface, the

device power can be lowered by about 20 mW by setting this bit. Use this mode only for Fs less than 40

MSPS. Refer to section Low power RX CMOS mode.

REG_SINGLE : Setting this bit power downs one ADC (Channel A) and One DAC (Channel A). The

output data format is SDR. In this mode DAC Channel B and ADC Channel B are active.

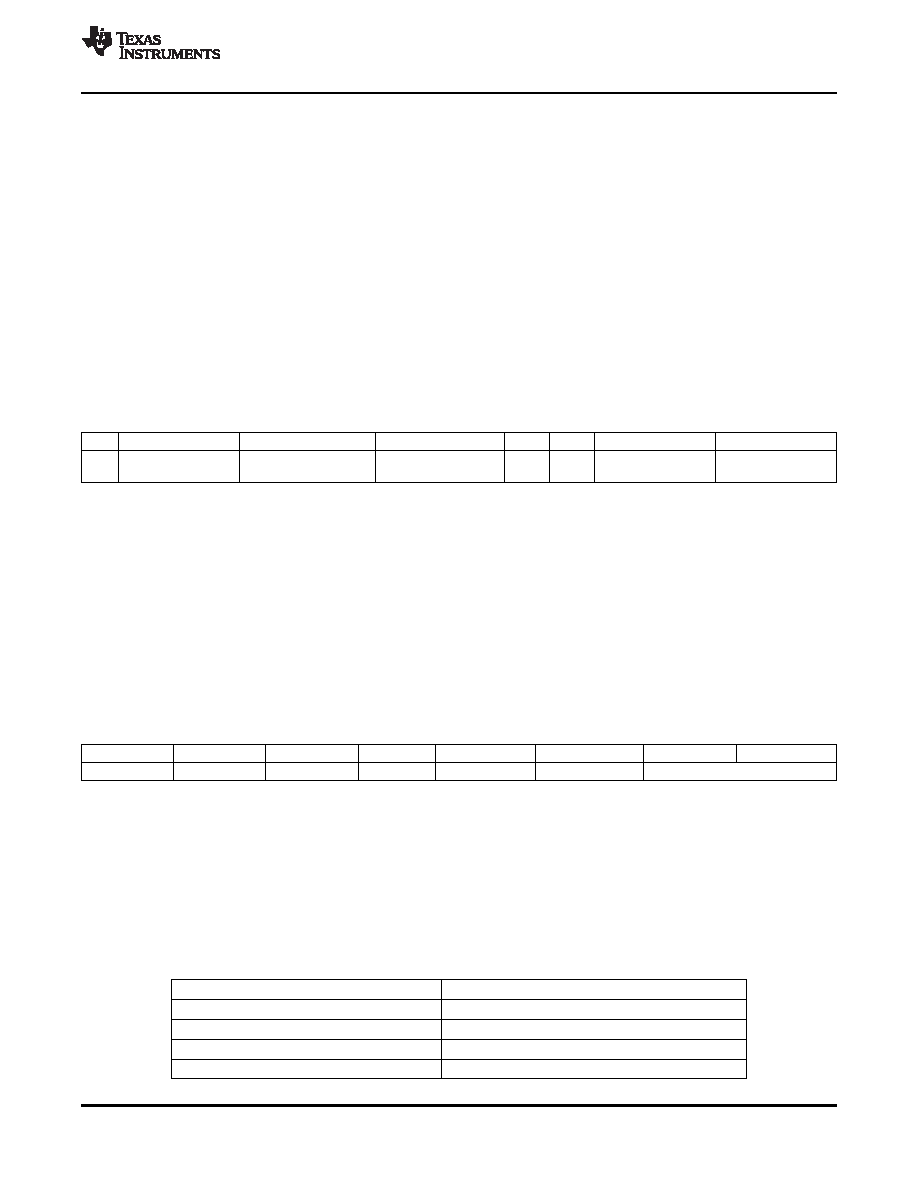

Register Name – CONFIG110 – Address 0x209, Default = 0x00

<7>

<6>

<5>

<4>

<3>

<2>

<1>

<0>

REG_OEZ_

LVDS_ CHB

LVDS_ CHA

LVDS_CLK

CMOS_ CLK

CMOS_DAT

REG_OEZ_CMOS_DAT: 3-state RX CMOS data buffers (use for Half Duplex TX mode when using

CMOS interface)

REG_OEZ_CMOS_CLK: 3-state RX CMOS clock buffer (use for Half Duplex TX mode when using CMOS

interface)

REG_OEZ_LVDS_CLK: 3-state RX LVDS clock buffer (use for Half Duplex TX mode when using LVDS

interface)

REG_OEZ_LVDS_CHA: 3-state RX LVDS data buffers for Channel A (use for Half Duplex TX mode when

using LVDS interface)

REG_OEZ_LVDS_CHB: 3-state RX LVDS data buffers for Channel B (use for Half Duplex TX mode when

using LVDS interface)

Register Name – CONFIG111 – Address 0x20A, Default = 0x00

<7>

<6>

<5>

<4>

<3>

<2>

<1>

<0>

REG_SE_CLK

REG_LVDS_TX

REG_LVDS_RX

WHAT_IS_SDOUT<1:0>

REG_SE_CLK: When set, the device is configured to expect two single ended clocks on CLKINP and

CLKINN. DAC_CLK gets derived from the clock on CLKINN and ADC_CLK from the clock on CLKINP.

The differential clock buffer is turned off, saving about 6mA of current on the 1.8 V supply.

REG_LVDS_TX: By default both RX and TX interfaces are in CMOS mode, this bit sets the TX input

interface in LVDS mode

REG_LVDS_RX: this bit sets the RX output interface in LVDS mode. In addition to setting this bit, also set

bit MASTER_OVERRIDE_RX (in CONFIG131) for proper LVDS settings.

WHAT_IS_SDOUT<1:0>: Configures the SDOUT pin.

WHAT_IS_SDOUT<1:0>

Mode

00

Floating

01

Analog test o/p (Do not use)

10

Digital o/p (Use for Aux ADC and register readout)

11

Digital i/p (Use for Aux DAC input mode)

Copyright 2011–2012, Texas Instruments Incorporated

REGISTER DESCRIPTIONS

45

相关PDF资料 |

PDF描述 |

|---|---|

| JKXFD0G07MSSDPGR | CONN PLUG 7POS CABLE PIN SLD |

| VE-B3W-IV | CONVERTER MOD DC/DC 5.5V 150W |

| VE-B3T-IV | CONVERTER MOD DC/DC 6.5V 150W |

| VI-J3L-MY-F2 | CONVERTER MOD DC/DC 28V 50W |

| VI-B6V-MX-F1 | CONVERTER MOD DC/DC 5.8V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AFE7222IRGCT | 功能描述:射频前端 Dual 12B,65MSPS ADC RoHS:否 制造商:Skyworks Solutions, Inc. 类型: 工作频率:2.4 GHz, 5 GHz 最大数据速率:54 Mbps 噪声系数: 工作电源电压:3.3 V 电源电流:180 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-32 |

| AFE7225 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Analog Front End Wideband Mixed-Signal Transceiver |

| AFE7225EVM | 功能描述:射频开发工具 AFE7225 Eval Mod RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| AFE7225IRGC25 | 功能描述:射频前端 Dual 12B,125MSPS ADC RoHS:否 制造商:Skyworks Solutions, Inc. 类型: 工作频率:2.4 GHz, 5 GHz 最大数据速率:54 Mbps 噪声系数: 工作电源电压:3.3 V 电源电流:180 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-32 |

| AFE7225IRGCR | 功能描述:射频前端 Dual 12B,125MSPS ADC RoHS:否 制造商:Skyworks Solutions, Inc. 类型: 工作频率:2.4 GHz, 5 GHz 最大数据速率:54 Mbps 噪声系数: 工作电源电压:3.3 V 电源电流:180 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-32 |

发布紧急采购,3分钟左右您将得到回复。