- 您现在的位置:买卖IC网 > PDF目录294981 > AGLN030V2-FUCG81 FPGA, PBGA81 PDF资料下载

参数资料

| 型号: | AGLN030V2-FUCG81 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, PBGA81 |

| 封装: | 4 X 4 MM, 0.80 MM HEIGHT, 0.40 MM PITCH, ROHS COMPLIANT, UCSP-81 |

| 文件页数: | 2/114页 |

| 文件大小: | 3991K |

| 代理商: | AGLN030V2-FUCG81 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页

IGLOO nano Device Overview

1- 6

A d vance v0.4

Flash*Freeze Technology

The IGLOO nano device has an ultra-low-power static mode, called Flash*Freeze mode, which

retains all SRAM and register information and can still quickly return to normal operation.

Flash*Freeze technology enables the user to quickly (within 1 s) enter and exit Flash*Freeze mode

by activating the Flash*Freeze pin while all power supplies are kept at their original values. I/Os,

global I/Os, and clocks can still be driven and can be toggling without impact on power

consumption, and the device retains all core registers, SRAM information, and I/O states. I/Os can

be individually configured to either hold their previous state or be tristated during Flash*Freeze

mode.

Alternatively, I/Os can be set to a specific state using weak pull-up or pull-down I/O attribute

configuration. No power is consumed by the I/O banks, clocks, JTAG pins, or PLL, and the device

consumes as little as 2 W in this mode.

Flash*Freeze technology allows the user to switch to Active mode on demand, thus simplifying the

power management of the device.

The Flash*Freeze pin (active low) can be routed internally to the core to allow the user's logic to

decide when it is safe to transition to this mode. Refer to Figure 1-5 for an illustration of

entering/exiting Flash*Freeze mode. It is also possible to use the Flash*Freeze pin as a regular I/O if

Flash*Freeze mode usage is not planned.

VersaTiles

The IGLOO nano core consists of VersaTiles, which have been enhanced beyond the ProASICPLUS

core tiles. The IGLOO nano VersaTile supports the following:

All 3-input logic functions—LUT-3 equivalent

Latch with clear or set

D-flip-flop with clear or set

Enable D-flip-flop with clear or set

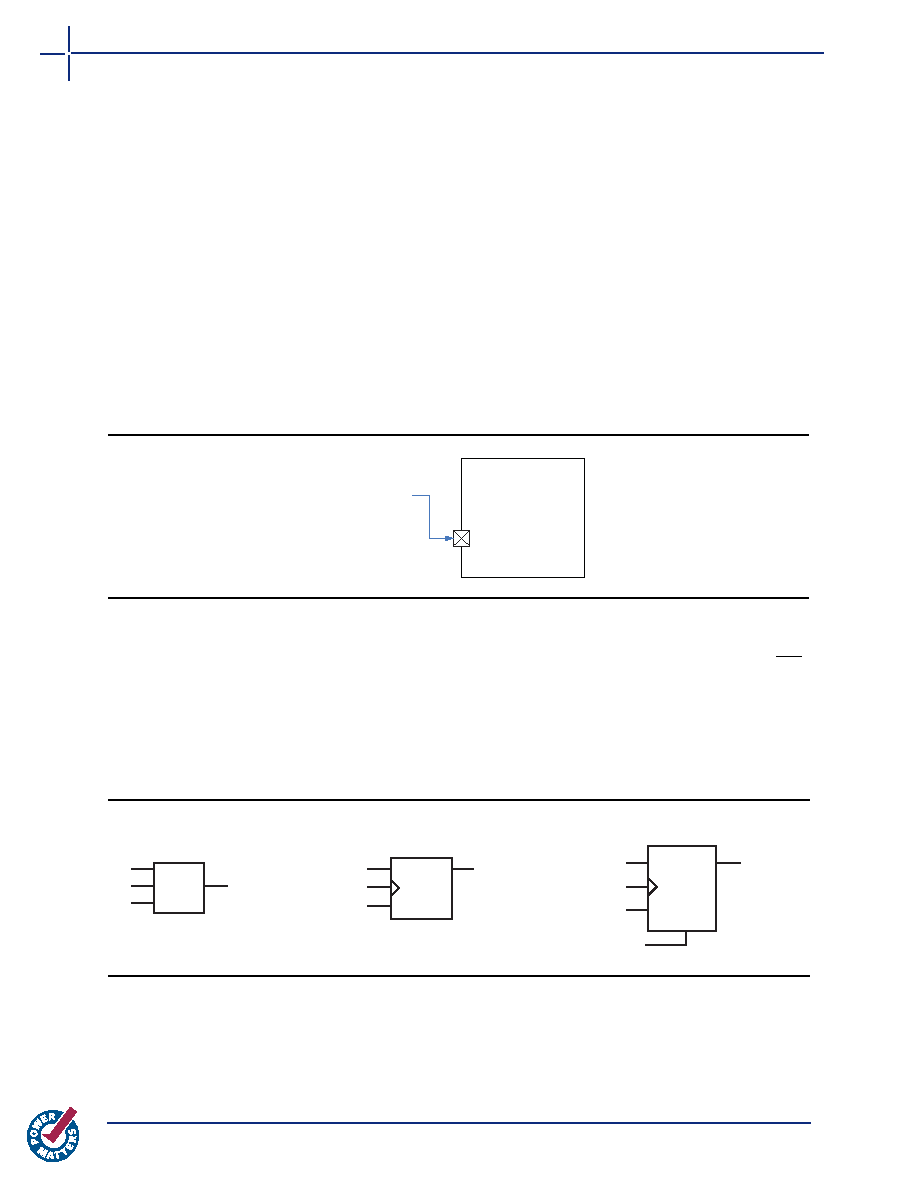

Refer to Figure 1-6 for VersaTile configurations.

Figure 1-5 IGLOO nano Flash*Freeze Mode

Actel IGLOO Nano

FPGA

Flash*Freeze

Mode Control

Flash*Freeze Pin

Figure 1-6 VersaTile Configurations

X1

Y

X2

X3

LUT-3

Data

Y

CLK

Enable

CLR

D-FF

Data

Y

CLK

CLR

D-FF

LUT-3 Equivalent

D-Flip-Flop with Clear or Set

Enable D-Flip-Flop with Clear or Set

相关PDF资料 |

PDF描述 |

|---|---|

| AGLN030V2-FVQ100 | FPGA, PQFP100 |

| AGLN030V2-FVQG100 | FPGA, PQFP100 |

| AGLN030V2-ZFCS81 | FPGA, PBGA81 |

| AGLN030V2-ZFCSG81 | FPGA, PBGA81 |

| AGLN030V2-ZFQN48 | FPGA, PQCC48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AGLN030V2-ZCSG81 | 功能描述:IC FPGA NANO 1KB 30K 81-CSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN030V2-ZCSG81I | 功能描述:IC FPGA NANO 1KB 30K 81-CSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN030V2-ZQNG48 | 功能描述:IC FPGA NANO 1KB 30K 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN030V2-ZQNG48I | 功能描述:IC FPGA NANO 1KB 30K 48-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| AGLN030V2-ZQNG68 | 功能描述:IC FPGA NANO 1KB 30K 68-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:IGLOO nano 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。