参数资料

| 型号: | APA300-FGG144A |

| 厂商: | Microsemi SoC |

| 文件页数: | 79/178页 |

| 文件大小: | 0K |

| 描述: | IC FPGA PROASIC+ 300K 144-FBGA |

| 标准包装: | 160 |

| 系列: | ProASICPLUS |

| RAM 位总计: | 73728 |

| 输入/输出数: | 100 |

| 门数: | 300000 |

| 电源电压: | 2.375 V ~ 2.625 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 144-LBGA |

| 供应商设备封装: | 144-FPBGA(13x13) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页当前第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页

ProASICPLUS Flash Family FPGAs

v5.9

2-7

Power-Up Sequencing

While ProASICPLUS devices are live at power-up, the order

of VDD and VDDP power-up is important during system

start-up. VDD should be powered up simultaneously with

VDDP on ProASIC

PLUS devices. Failure to follow these

guidelines may result in undesirable pin behavior during

system start-up. For more information, refer to Actel’s

Power-Up Behavior of ProASICPLUS Devices application

note.

LVPECL Input Pads

In addition to standard I/O pads and power pads,

ProASICPLUS devices have a single LVPECL input pad on

both the east and west sides of the device, along with

AVDD and AGND pins to power the PLL block. The

LVPECL pad cell consists of an input buffer (containing a

low voltage differential amplifier) and a signal and its

complement, PPECL (I/P) (PECLN) and NPECL (PECLREF).

The LVPECL input pad cell differs from the standard I/O

cell in that it is operated from VDD only.

Since it is exclusively an input, it requires no output

signal, output enable signal, or output configuration

bits. As a special high-speed differential input, it also

does not require pull-ups. Recommended termination

for LVPECL inputs is shown in Figure 2-7. The LVPECL pad

cell compares voltages on the PPECL (I/P) pad (as

illustrated in Figure 2-8) and the NPECL pad and sends

the results to the global MUX (Figure 2-11 on page 2-11).

This high-speed, low-skew output essentially controls the

clock conditioning circuit.

LVPECLs are designed to meet LVPECL JEDEC receiver

standard levels (Table 2-5).

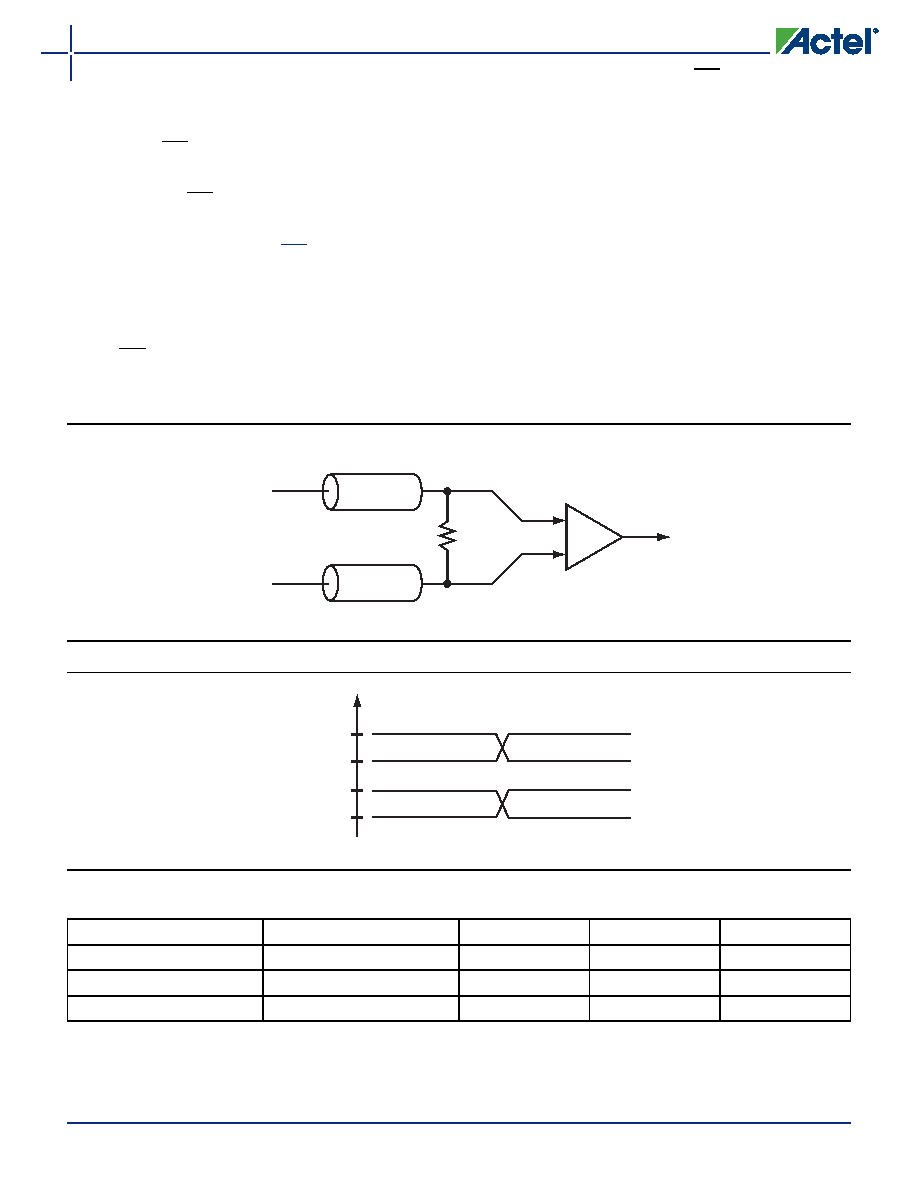

Figure 2-7 Recommended Termination for LVPECL Inputs

Figure 2-8 LVPECL High and Low Threshold Values

Table 2-5

LVPECL Receiver Specifications

Symbol

Parameter

Minimum

Maximum

Units

VIH

Input High Voltage

1.49

2.72

V

VIL

Input Low Voltage

0.86

2.125

V

VID

Differential Input Voltage

0.3

VDD

V

+

_

PPECL

NPECL

From LVPECL Driver

Data

Z = 50

Ω

0

Z = 50

Ω

0

R = 100

Ω

2.72

2.125

1.49

0.86

Voltage

相关PDF资料 |

PDF描述 |

|---|---|

| AX500-FGG484 | IC FPGA AXCELERATOR 500K 484FBGA |

| A3P1000L-FGG484I | IC FPGA 1KB FLASH 1M 484-FBGA |

| M1A3P1000L-FGG484I | IC FPGA M1 1KB FLASH 1M 484FBGA |

| A3P1000L-FG484I | IC FPGA 1KB FLASH 1M 484-FBGA |

| M1A3P1000L-FG484I | IC FPGA M1 1KB FLASH 1M 484FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| APA300-FGG144I | 功能描述:IC FPGA PROASIC+ 300K 144-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASICPLUS 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| APA300-FGG144M | 制造商:Microsemi Corporation 功能描述:FPGA PROASICPLUS 300K GATES 180MHZ 0.22UM 2.5V 144FBGA - Trays |

| APA300-FGG256 | 功能描述:IC FPGA PROASIC+ 300K 256-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASICPLUS 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| APA300-FGG256A | 功能描述:IC FPGA PROASIC+ 300K 256-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASICPLUS 产品培训模块:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色产品:Cyclone? IV FPGAs 标准包装:60 系列:CYCLONE® IV GX LAB/CLB数:9360 逻辑元件/单元数:149760 RAM 位总计:6635520 输入/输出数:270 门数:- 电源电压:1.16 V ~ 1.24 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:484-BGA 供应商设备封装:484-FBGA(23x23) |

| APA300-FGG256I | 功能描述:IC FPGA PROASIC+ 300K 256-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASICPLUS 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

发布紧急采购,3分钟左右您将得到回复。