参数资料

| 型号: | APA600-FG676 |

| 厂商: | Microsemi SoC |

| 文件页数: | 90/178页 |

| 文件大小: | 0K |

| 描述: | IC FPGA PROASIC+ 600K 676-FBGA |

| 标准包装: | 40 |

| 系列: | ProASICPLUS |

| RAM 位总计: | 129024 |

| 输入/输出数: | 454 |

| 门数: | 600000 |

| 电源电压: | 2.3 V ~ 2.7 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 676-BGA |

| 供应商设备封装: | 676-FBGA(27x27) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页当前第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页

ProASICPLUS Flash Family FPGAs

v5.9

2-9

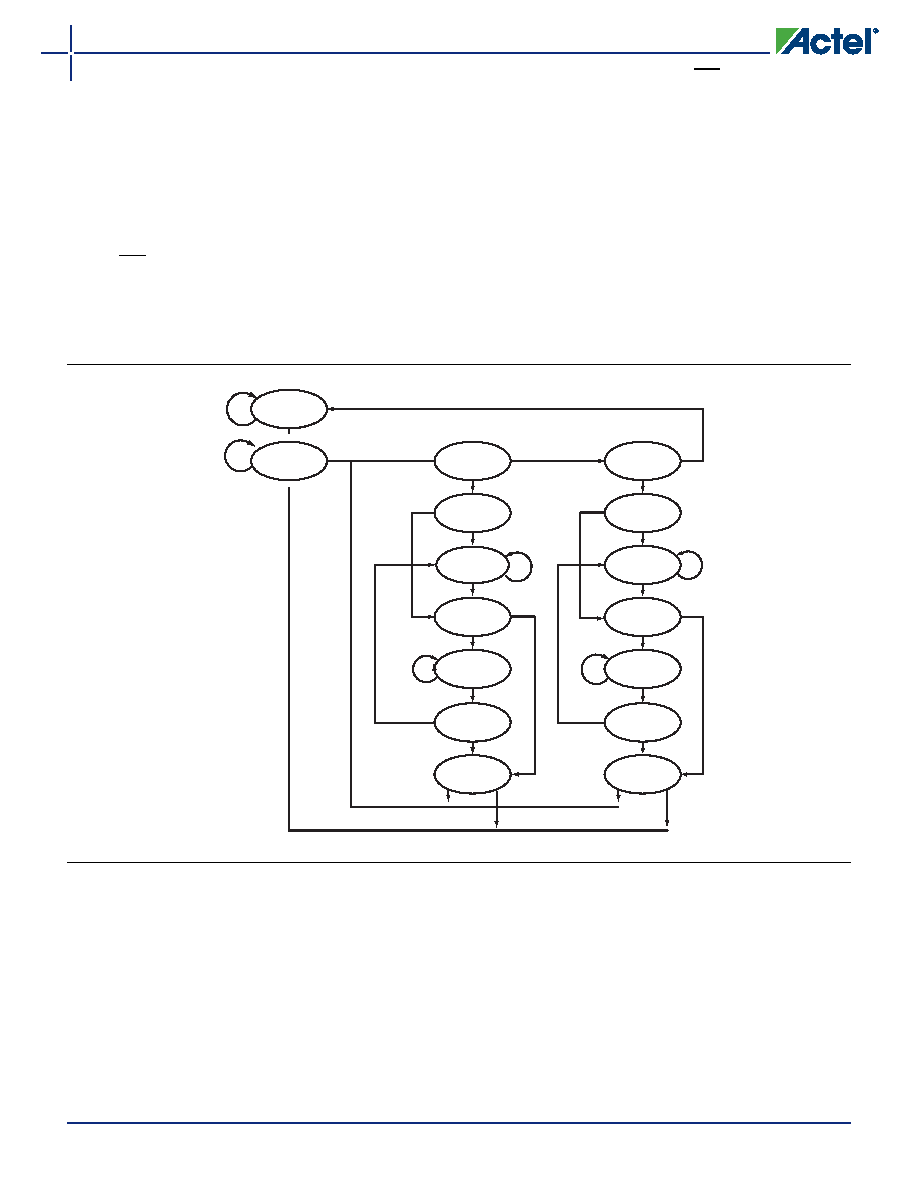

The TAP controller receives two control inputs (TMS and

TCK) and generates control and clock signals for the rest

of the test logic architecture. On power-up, the TAP

controller enters the Test-Logic-Reset state. To guarantee

a reset of the controller from any of the possible states,

TMS must remain high for five TCK cycles. The TRST pin

may also be used to asynchronously place the TAP

controller in the Test-Logic-Reset state.

ProASICPLUS devices support three types of test data

registers: bypass, device identification, and boundary

scan. The bypass register is selected when no other

register needs to be accessed in a device. This speeds up

test data transfer to other devices in a test data path.

The 32-bit device identification register is a shift register

with four fields (lowest significant byte (LSB), ID number,

part number and version). The boundary-scan register

observes and controls the state of each I/O pin.

Each I/O cell has three boundary-scan register cells, each

with a serial-in, serial-out, parallel-in, and parallel-out

pin. The serial pins are used to serially connect all the

boundary-scan register cells in a device into a boundary-

scan register chain, which starts at the TDI pin and ends

at the TDO pin. The parallel ports are connected to the

internal core logic tile and the input, output, and control

ports of an I/O buffer to capture and load data into the

register to control or observe the logic state of each I/O.

Figure 2-10 TAP Controller State Diagram

Test-Logic

Reset

Run-Test/

Idle

Select-DR-

Scan

Capture-DR

Shift-DR

Exit-DR

Pause-DR

Exit2-DR

Update-DR

Select-IR-

Scan

Capture-IR

Shift-IR

Exit-IR

Pause-IR

Exit2-IR

Update-IR

1

0

1

0

00

1

00

1

0

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| ASM44DSES-S243 | CONN EDGECARD 88POS .156 EYELET |

| FMM22DSEF | CONN EDGECARD 44POS .156 EYELET |

| APA600-FGG676 | IC FPGA PROASIC+ 600K 676-FBGA |

| M1AFS600-1FGG484K | IC FPGA 4MB FLASH 600K 484-FBGA |

| M1AFS600-1FG484K | IC FPGA 4MB FLASH 600K 484-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| APA600-FG676I | 功能描述:IC FPGA PROASIC+ 600K 676-FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASICPLUS 标准包装:1 系列:ProASICPLUS LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:129024 输入/输出数:248 门数:600000 电源电压:2.3 V ~ 2.7 V 安装类型:表面贴装 工作温度:- 封装/外壳:352-BFCQFP,带拉杆 供应商设备封装:352-CQFP(75x75) |

| APA600-FG896A | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:Automotive-Grade ProASIC Flash Family FPGAs |

| APA600-FGB | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA600-FGES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA600-FGG256 | 功能描述:IC FPGA PROASIC+ 600K 256-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:ProASICPLUS 产品培训模块:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色产品:Cyclone? IV FPGAs 标准包装:60 系列:CYCLONE® IV GX LAB/CLB数:9360 逻辑元件/单元数:149760 RAM 位总计:6635520 输入/输出数:270 门数:- 电源电压:1.16 V ~ 1.24 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:484-BGA 供应商设备封装:484-FBGA(23x23) |

发布紧急采购,3分钟左右您将得到回复。