- 您现在的位置:买卖IC网 > Datasheet目录316 > BU99901GUZ-WE2 (Rohm Semiconductor)IC EEPROM 32KBIT 2WIRE VCSP Datasheet资料下载

参数资料

| 型号: | BU99901GUZ-WE2 |

| 厂商: | Rohm Semiconductor |

| 文件页数: | 16/26页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 32KBIT 2WIRE VCSP |

| 标准包装: | 3,000 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 32K (4K x 8) |

| 速度: | 400kHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.7 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 6-XFBGA,CSPBGA |

| 供应商设备封装: | VCSP30L1 |

| 包装: | 带卷 (TR) |

�� �

�

BU99901GUZ-W� (32Kbit)�

�Datasheet�

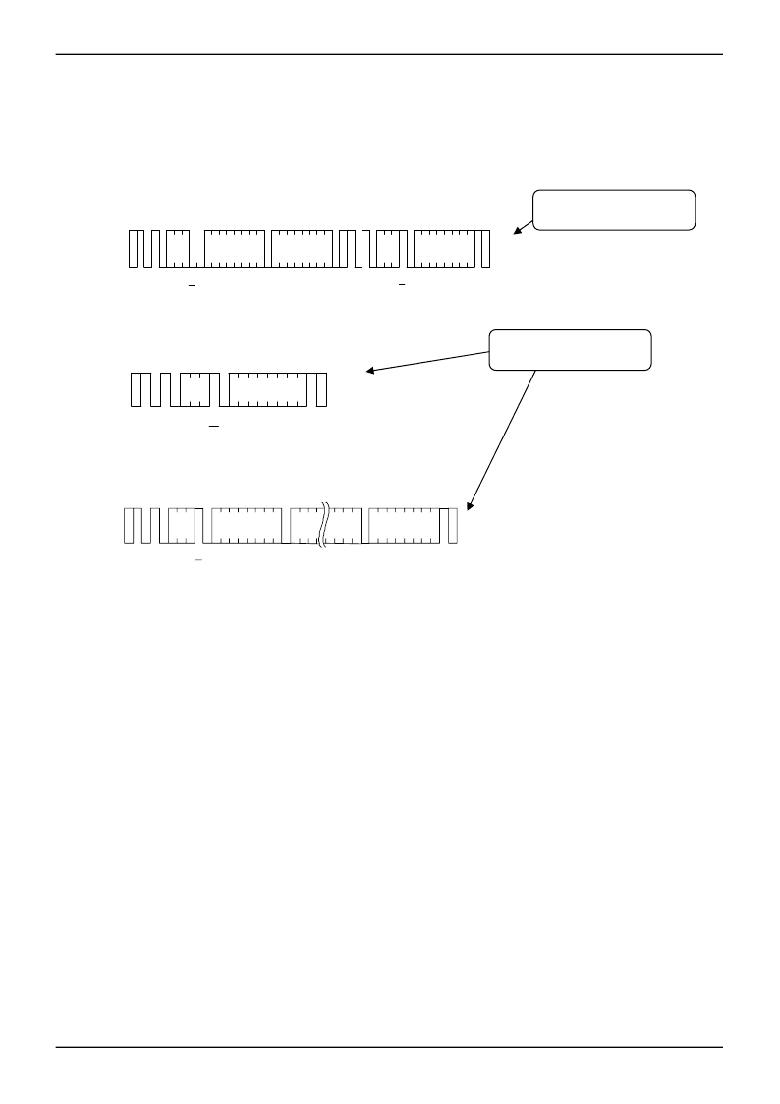

�●� Read� Command�

�○� Read� cycle�

�Data� of� EEPROM� is� read.� In� read� cycle,� there� are� random� read� cycle� and� current� read� cycle.�

�Random� read� cycle� is� a� command� to� read� data� by� designating� address,� and� is� used� generally.�

�Current� read� cycle� is� a� command� to� read� data� of� internal� address� register� without� designating� address,� and� is� used� when�

�to� verify� just� after� write� cycle.� In� both� the� read� cycles,� sequential� read� cycle� is� available,� and� the� next� address� data� can�

�be� read� in� succession.�

�SDA�

�LINE�

�S�

�T�

�A�

�R�

�T�

�SLAVE�

�ADDRESS�

�1� 0�

�1� 0� 0� 0� 0�

�W�

�R�

�I�

�T�

�E�

�1st� WORD�

�ADDRESS(n)�

�*� *� *� *� WA�

�11�

�2nd� WORD�

�ADDRESS(n)�

�WA�

�0�

�S�

�T�

�A�

�R�

�T�

�SLAVE�

�ADDRESS�

�1� 0�

�1� 0� A� 2� A1� A0�

�R�

�E�

�A�

�D�

�D7�

�DATA(n)�

�D0�

�S�

�T�

�O�

�P�

�It� is� necessary� to� input� 'H'�

�to� the� last� ACK.�

�R� A�

�/� C�

�W� K�

�A�

�C�

�K�

�A�

�C�

�K�

�R� A�

�/� C�

�W� K�

�A�

�C�

�K�

�Figure� 36.� Random� read� cycle�

�S�

�T�

�A�

�R�

�T�

�S� LA� V� E�

�ADDRESS�

�R�

�E�

�A�

�D�

�D� A� TA� (n� )�

�S�

�T�

�O�

�P�

�It� is� necessary� to� input� 'H'�

�to� the� last� ACK.�

�SDA�

�L� IN� E�

�1� 0� 1� 0� 0� 0� 0�

�R� A�

�/� C�

�W� K�

�D7�

�D0�

�A�

�C�

�K�

�Figure� 37.� Current� read� cycle�

�S�

�T�

�A�

�R�

�T�

�SLAVE�

�ADDRESS�

�R�

�E�

�A�

�D�

�DATA(n)�

�DATA(n+x)�

�S�

�T�

�O�

�P�

�SDA�

�LINE�

�1� 0� 1� 0� 0� 0� 0�

�R� A�

�/� C�

�W� K�

�D7�

�D0�

�A�

�C�

�K�

�A�

�C�

�K�

�D7�

�D0�

�A�

�C�

�K�

�Figure� 38.� Sequential� read� cycle� (in� the� case� of� current� read� cycle)�

�?� In� random� read� cycle,� data� of� designated� word� address� can� be� read.�

�?� When� the� command� just� before� current� read� cycle� is� random� read� cycle,� current� read� cycle� (each� including� sequential�

�read� cycle),� data� of� incremented� last� read� address� (n)-th� address,� i.e.,� data� of� the� (n+1)-th� address� is� output.�

�?� When� ACK� signal� 'LOW'� after� D0� is� detected,� and� stop� condition� is� not� sent� from� master� (μ-COM)� side,� the� next�

�address� data� can� be� read� in� succession.�

�?� Read� cycle� is� ended� by� stop� condition� where� 'H'� is� input� to� ACK� signal� after� D0� and� SDA� signal� is� started� at� SCL�

�signal� 'H'.�

�?� When� 'H'� is� not� input� to� ACK� signal� after� D0,� sequential� read� gets� in,� and� the� next� data� is� output.�

�Therefore,� read� command� cycle� cannot� be� ended.� When� to� end� read� command� cycle,� be� sure� input� stop� condition� to�

�input� 'H'� to� ACK� signal� after� D0,� and� to� start� SDA� at� SCL� signal� 'H'.�

�?� Sequential� read� is� ended� by� stop� condition� where� 'H'� is� input� to� ACK� signal� after� arbitrary� D0� and� SDA� is� started� at� SCL�

�signal� 'H'.�

�www.rohm.com�

�?� 2012� ROHM� Co.,� Ltd.� All� rights� reserved.�

�TSZ22111� ?� 15� ?� 001�

�16/23�

�TSZ02201-0R2R0G100280-1-2�

�4.SEP.2012� Rev.001�

�相关PDF资料 |

PDF描述 |

|---|---|

| BUK218-50DY,118 | TOPFET DUAL SWITCH D2PAK |

| BVL121200003N | BATTERY CHG UNIV 12VDC @ 1.2A |

| BVW241250003A | BATTERY CHG UNIV 24VDC @ 1.25A |

| C-14245 | RACKMOUNT INTERNAL CHASSIS |

| C-1555 | CABINET SLOPING PANEL PRESTIGE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU9H-103R25BL | 制造商:Coilcraft Inc 功能描述:Common mode choke, power line, RoHS |

| BU9H-1320R7BL | 制造商:Coilcraft Inc 功能描述:Common mode choke, power line, RoHS |

| BU9H-2011R6BL | 制造商:Coilcraft Inc 功能描述:Common mode choke, power line, RoHS |

| BU9H-2820R5BL | 制造商:Coilcraft Inc 功能描述:Common mode choke, power line, RoHS |

| BU9H-6011R0BL | 制造商:Coilcraft Inc 功能描述:Common mode choke, power line, RoHS |

发布紧急采购,3分钟左右您将得到回复。