- 您现在的位置:买卖IC网 > PDF目录379948 > COP8SGA040N9 (National Semiconductor Corporation) 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART PDF资料下载

参数资料

| 型号: | COP8SGA040N9 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| 中文描述: | 8位的CMOS基于ROM和OTP微控制器具有8K到32K的内存,2个比较器和USART |

| 文件页数: | 22/62页 |

| 文件大小: | 913K |

| 代理商: | COP8SGA040N9 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

5.0 Functional Description

(Continued)

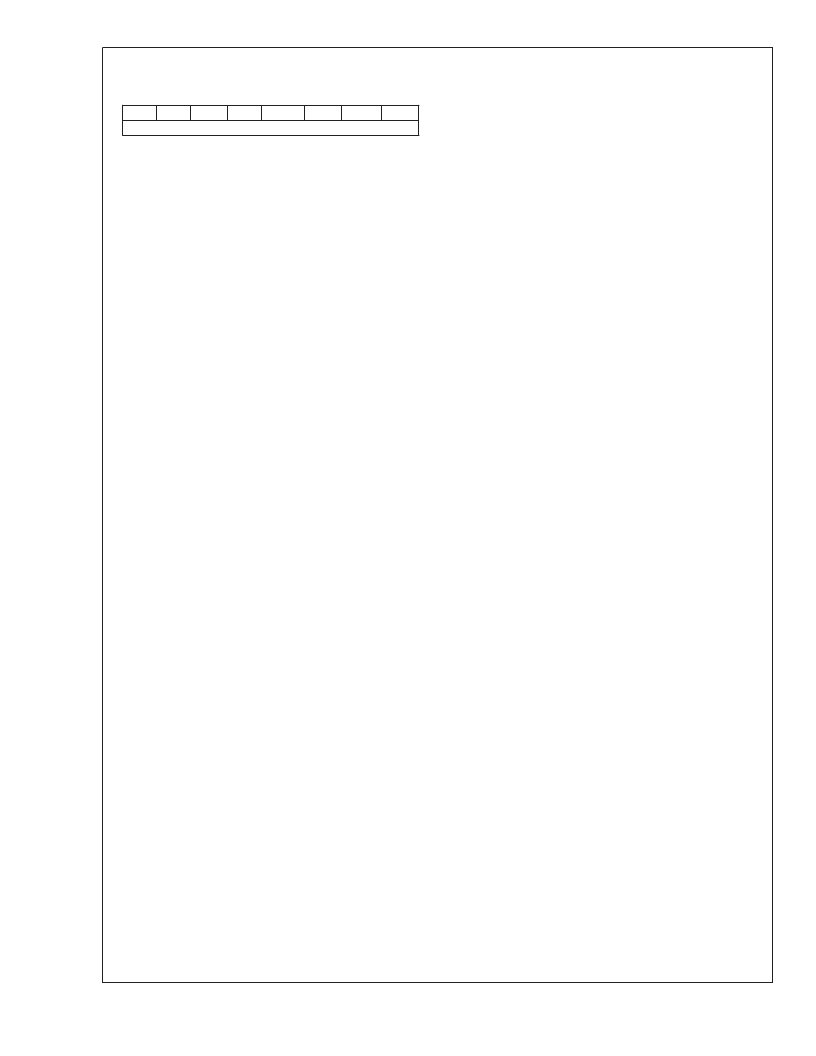

T3CNTRL Register (Address X'00B6)

T3C3

T3C2

T3C1

T3C0

T3PNDA

T3ENA

T3PNDB

T3ENB

Bit 7

Bit 0

The T3CNTRL control register contains the following bits:

T3C3

Timer T3 mode control bit

T3C2

Timer T3 mode control bit

T3C1

Timer T3 mode control bit

T3C0

Timer

T3

Start/Stop

modes 1 and 2, T3 Underflow Interrupt Pend-

ing Flag in timer mode 3

T3PNDA Timer T3 Interrupt Pending Flag (Autoreload

RA in mode 1, T3 Underflow in mode 2, T3A

capture edge in mode 3)

T3ENA

Timer T3 Interrupt Enable for Timer Underflow

or T3A Input capture edge

T3PNDB Timer T3 Interrupt Pending Flag for T3B cap-

ture edge

T3ENB

Timer T3 Interrupt Enable for Timer Underflow

or T3B Input capture edge

control

in

timer

6.0 Timers

Each device contains a very versatile set of timers (T0, T1,

T2 and T3). Timer T1, T2 and T3 and associated autoreload/

capture registers power up containing random data.

6.1 TIMER T0 (IDLE TIMER)

Each device supports applications that require maintaining

real time and low power with the IDLE mode. This IDLE

mode support is furnished by the IDLE timer T0. The Timer

T0 runs continuously at the fixed rate of the instruction cycle

clock, t

C

. The user cannot read or write to the IDLE Timer T0,

which is a count down timer.

The Timer T0 supports the following functions:

Exit out of the Idle Mode (See Idle Mode description)

WATCHDOG logic (See WATCHDOG description)

Start up delay out of the HALT mode

Timing the width of the internal power-on-reset

The IDLE Timer T0 can generate an interrupt when the

twelfth bit toggles. This toggle is latched into the T0PND

pending flag, and will occur every 2.731 ms at the maximum

clock frequency (t

= 0.67 μs).Acontrol flag T0EN allows the

interrupt from the twelfth bit of Timer T0 to be enabled or

disabled. Setting T0EN will enable the interrupt, while reset-

ting it will disable the interrupt.

6.2 TIMER T1, TIMER T2 and TIMER T3

Each device have a set of three powerful timer/counter

blocks, T1, T2 and T3. Since T1, T2, and T3 are identical, all

comments are equally applicable to any of the three timer

blocks which will be referred to as Tx.

Each timer block consists of a 16-bit timer, Tx, and two

supporting 16-bit autoreload/capture registers, RxA and

RxB. Each timer block has two pins associated with it, TxA

and TxB. The pin TxA supports I/O required by the timer

block, while the pin TxB is an input to the timer block. The

timer block has three operating modes: Processor Indepen-

dent PWM mode, External Event Counter mode, and Input

Capture mode.

The control bits TxC3, TxC2, and TxC1 allow selection of the

different modes of operation.

6.2.1 Mode 1. Processor Independent PWM Mode

One of the timer’s operating modes is the Processor Inde-

pendent PWM mode. In this mode, the timer generates a

“Processor Independent” PWM signal because once the

timer is setup, no more action is required from the CPU

which translates to less software overhead and greater

throughput. The user software services the timer block only

when the PWM parameters require updating. This capability

is provided by the fact that the timer has two separate 16-bit

reload registers. One of the reload registers contains the

“ON” timer while the other holds the “OFF” time. By contrast,

a microcontroller that has only a single reload register re-

quires an additional software to update the reload value

(alternate between the on-time/off-time).

The timer can generate the PWM output with the width and

duty cycle controlled by the values stored in the reload

registers. The reload registers control the countdown values

and the reload values are automatically written into the timer

when it counts down through 0, generating interrupt on each

reload. Under software control and with minimal overhead,

the PMW outputs are useful in controlling motors, triacs, the

intensity of displays, and in providing inputs for data acqui-

sition and sine wave generators.

In this mode, the timer Tx counts down at a fixed rate of t

.

Upon every underflow the timer is alternately reloaded with

the contents of supporting registers, RxA and RxB. The very

first underflow of the timer causes the timer to reload from

the register RxA. Subsequent underflows cause the timer to

be reloaded from the registers alternately beginning with the

register RxB.

Figure 15shows a block diagram of the timer in PWM mode.

The underflows can be programmed to toggle the TxAoutput

pin. The underflows can also be programmed to generate

interrupts.

Underflows from the timer are alternately latched into two

pending flags, TxPNDA and TxPNDB. The user must reset

these pending flags under software control. Two control

enable flags, TxENA and TxENB, allow the interrupts from

the timer underflow to be enabled or disabled. Setting the

timer enable flag TxENA will cause an interrupt when a timer

underflow causes the RxA register to be reloaded into the

timer. Setting the timer enable flag TxENB will cause an

interrupt when a timer underflow causes the RxB register to

be reloaded into the timer. Resetting the timer enable flags

will disable the associated interrupts.

Either or both of the timer underflow interrupts may be

enabled. This gives the user the flexibility of interrupting

once per PWM period on either the rising or falling edge of

the PWM output. Alternatively, the user may choose to inter-

rupt on both edges of the PWM output.

6.2.2 Mode 2. External Event Counter Mode

This mode is quite similar to the processor independent

PWM mode described above. The main difference is that the

timer, Tx, is clocked by the input signal from the TxApin. The

Tx timer control bits, TxC3, TxC2 and TxC1 allow the timer to

be clocked either on a positive or negative edge from the

TxA pin. Underflows from the timer are latched into the

TxPNDA pending flag. Setting the TxENA control flag will

cause an interrupt when the timer underflows.

C

www.national.com

22

相关PDF资料 |

PDF描述 |

|---|---|

| COP8SGA040Q3 | LMH0046 HD/SD SDI Reclocker with Dual Differential Outputs; Package: TSSOP EXP PAD; No of Pins: 20 |

| COP8SGA040Q6 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q7 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q8 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q9 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

相关代理商/技术参数 |

参数描述 |

|---|---|

| COP8SGA040Q3 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q6 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q7 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q8 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGA040Q9 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

发布紧急采购,3分钟左右您将得到回复。