- 您现在的位置:买卖IC网 > PDF目录16067 > COREPCIF-OM (Microsemi SoC)IP MODULE COREPCIF PDF资料下载

参数资料

| 型号: | COREPCIF-OM |

| 厂商: | Microsemi SoC |

| 文件页数: | 63/156页 |

| 文件大小: | 0K |

| 描述: | IP MODULE COREPCIF |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页当前第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页

�� �

�

�

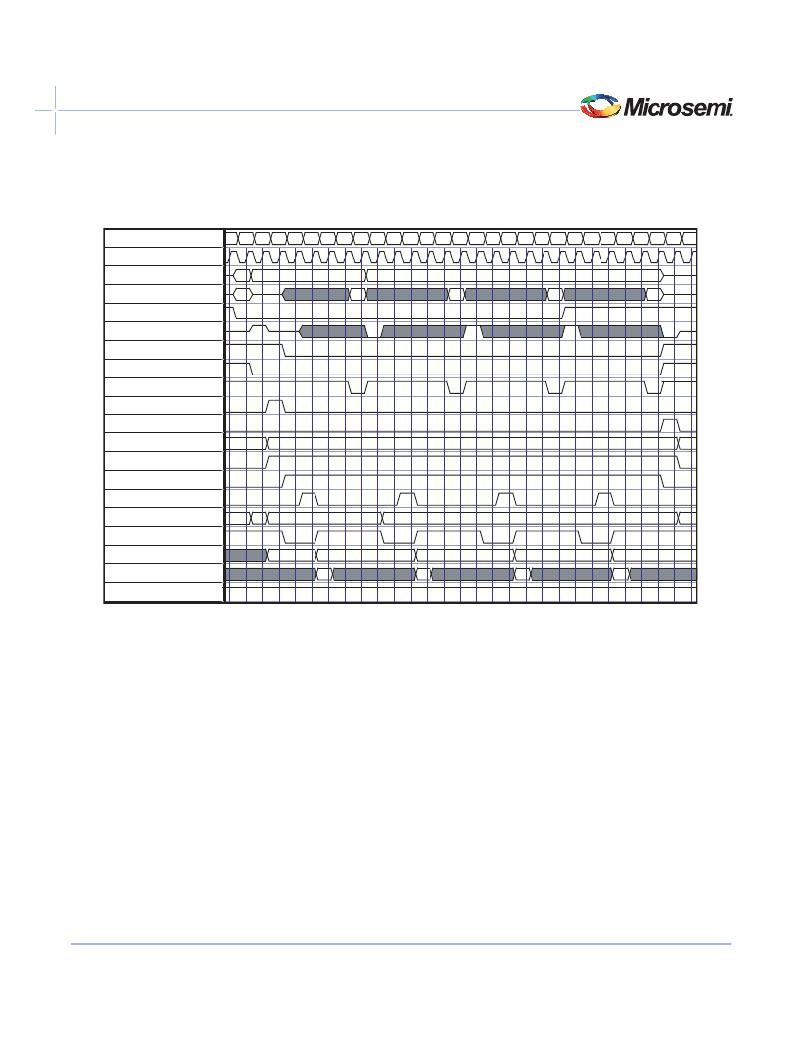

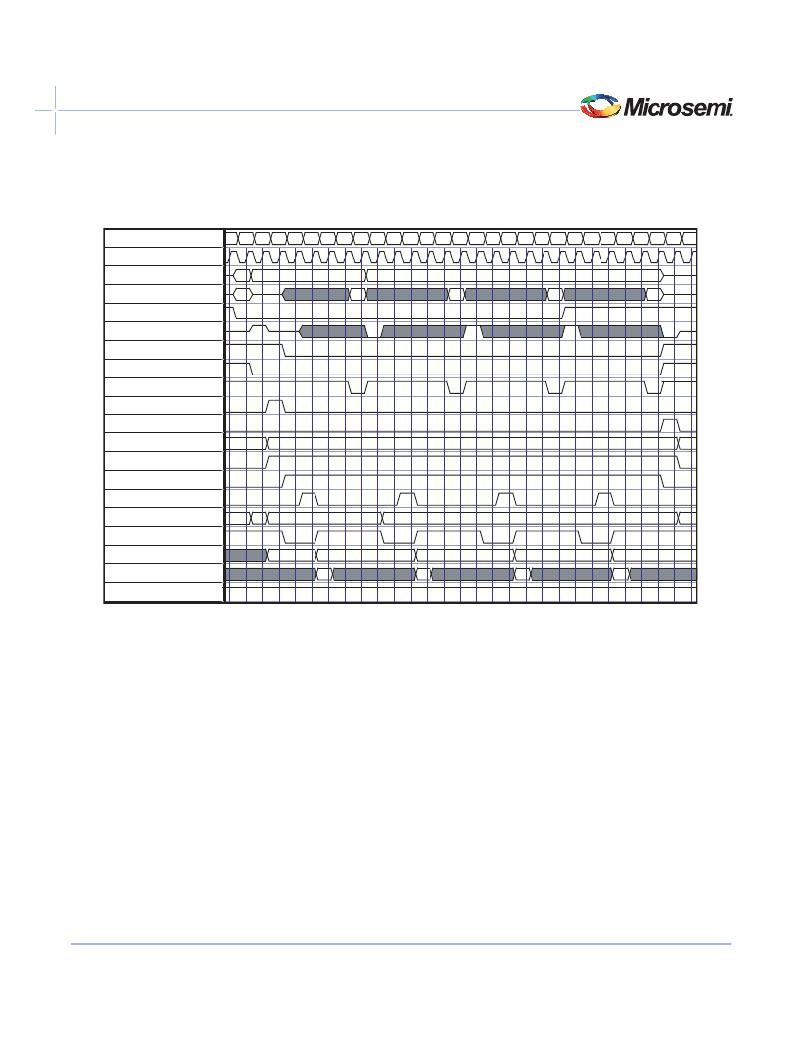

�Burst� Transfer� with� FIFO� Recovery� Enabled�

�Burst� Transfer� with� FIFO� Recovery� Enabled�

�CorePCIF� directly� supports� connection� of� external� FIFOs.� When� FIFOs� are� connected� to� the� core,� special� logic� is�

�implemented� inside� the� core� to� prevent� data� loss.� As� seen� in� Figure� 6-10� on� page� 59� to� Figure� 6-12� on� page� 61� ,� the� core�

�reads� ahead� of� the� transfer� on� the� PCI� bus� during� a� burst� transfer� so� it� can� maintain� high� throughput.� This� is� illustrated�

�in� Figure� 6-5� on� page� 56� .� The� core� actually� transfers� four� words� on� the� PCI� bus� but� reads� seven� from� the� backend�

�interface.� Without� the� optional� FIFO� recovery� logic,� these� additional� three� words� would� be� lost.�

�When� the� FIFO� recovery� mode� is� enabled,� BAR� i� _ENABLE� =� 2.� The� core� will� store� these� three� words� internally� and�

�transfer� them� at� the� start� of� the� next� read� cycle� from� the� same� BAR.� Figure� 6-14� shows� an� initial� burst� read� cycle,�

�followed� by� a� second� read� cycle� that� initially� transfers� data� stored� from� the� first� transfer.�

�cycle�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�clk�

�framen�

�cben[3:0]�

�6�

�0�

�6�

�0�

�ad[31:0]�

�ADDR�

�0�

�1�

�2�

�3�

�ADDR�

�4�

�5�

�6�

�7�

�par�

�devseln�

�irdyn�

�trdyn�

�dp_start�

�dp_done�

�bar_select[2:0]�

�0�

�7�

�0�

�rd_cyc�

�rd_stb_out�

�rd_stb_in�

�mem_add[7:0]�

�00�

�04� 08� 0C� 10� 14�

�18�

�00�

�04�

�08�

�0C�

�mem_data_in[31:0]�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�rd_sync�

�Figure� 6-14� ·� FIFO� Recovery� Operation� (RD_SYNC� =� 0)�

�During� the� first� read� cycle,� as� shown� in� Figure� 6-14� ,� the� core� reads� six� words� from� the� backend� but� only� transfers� four�

�words� on� the� PCI� bus.� The� remaining� two� words,� four� and� five,� are� stored� in� the� core.� On� the� second� PCI� burst� read�

�cycle,� the� core� reads� the� next� data� words,� six� and� seven,� from� the� backend� before� it� stops� to� prevent� its� internal� storage�

�from� overflowing.� At� cycle� five� in� the� second� PCI� cycle,� word� four� is� transferred� on� the� PCI� bus.� When� the� second� PCI�

�cycle� terminates,� words� eight� and� nine� are� left� stored� in� the� core.�

�When� RD_SYNC� =� 1,� a� very� similar� pair� of� transfers� occurs,� but� in� this� case,� the� first� transfer� actually� reads� seven� words�

�and� transfers� four� words� on� the� bus,� leaving� three� words� stored� in� the� core� between� the� transfers.�

�v4.0�

�63�

�相关PDF资料 |

PDF描述 |

|---|---|

| 175101-R2-03.00 | CABLE .141 N TYPE PLUG-PLUG 3" |

| M3CFK-4018J | IDC CABLE - MKC40K/MC40G/MCF40K |

| M3CGK-4018J | IDC CABLE - MKC40K/MC40G/MCS40K |

| M3CEK-4018J | IDC CABLE - MKC40K/MC40G/MCE40K |

| M3AFK-4018J | IDC CABLE - MSC40K/MC40G/MCF40K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| COREPCIF-OMFL | 功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1 |

| COREPCIF-RM | 功能描述:IP MODULE COREPCIF RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| COREPCIF-RMFL | 功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1 |

| COREPCIF-UR | 功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1 |

| COREPCI-SN | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41 |

发布紧急采购,3分钟左右您将得到回复。