- 您现在的位置:买卖IC网 > PDF目录380066 > CS4218-KL (CRYSTAL SEMICONDUCTOR CORP) 16-Bit Stereo Audio Codec PDF资料下载

参数资料

| 型号: | CS4218-KL |

| 厂商: | CRYSTAL SEMICONDUCTOR CORP |

| 元件分类: | 消费家电 |

| 英文描述: | 16-Bit Stereo Audio Codec |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 18/44页 |

| 文件大小: | 586K |

| 代理商: | CS4218-KL |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Master Sub-Mode (SM3-M)

Master sub-mode is selected by setting

MF4:MA = 1, which configures SSYNC and

SCLK as outputs from the CS4218. During

power down, SSYNC and SCLK are driven high

impedance, and during reset they both are driven

low. In Master sub-mode the number of bits per

frame determines how many codecs can occupy

the serial bus and is illustrated in Figure 14.

Bits Per Frame (Master Sub-Modes)

MF8:SFS2 selects the number of bits per frame.

The two options are MF8:SFS2 = 1 which se-

lects 128 bits per frame, and MF8:SFS2 = 0

which selects 64 bits per frame.

Selecting 128 bits per frame (MF8:SFS2 = 1) al-

lows two CS4218s to operate from the same

serial bus since each codec requires 64 bit peri-

ods. The sub-frame used by an individual codec

is selected using MF7:SFS1. MF7:SFS1 = 0 se-

lects sub-frame 1 which is the first 64 bits

following the SSYNC pulse. MF7:SFS1 = 1 se-

lects sub-frame 2 which is the last 64 bits of the

frame.

Selecting 64 bits per frame (MF8:SFS2 = 0) al-

lows only one CS4218 to occupy the serial port.

Since there is only one sub-frame (which is

equal to one frame), MF7:SFS1 is defined differ-

ently in this mode. MF7:SFS1 selects the format

of SSYNC. MF7:SFS1 = 0 selects an SSYNC

pulse one SCLK period high, directly preceding

the data as shown in the center portion of Fig-

ure 14. This format is used for all other master

and slave sub-modes in SM3. If MF7:SFS1 = 1,

an alternate SSYNC format is chosen in which

SSYNC is high during the entire Word A

(32 bits), which includes the left sample, and

low for the entire Word B (32 bits), which in-

cludes the right sample. This alternate format for

SSYNC is illustrated in the bottom portion of

Figure 14 and is only available in SM3-M and

SM3-MM sub-modes with 64 bits per frame. A

more detailed timing diagram for the 64 bits-per-

frame master sub-modes is shown in Figure 15.

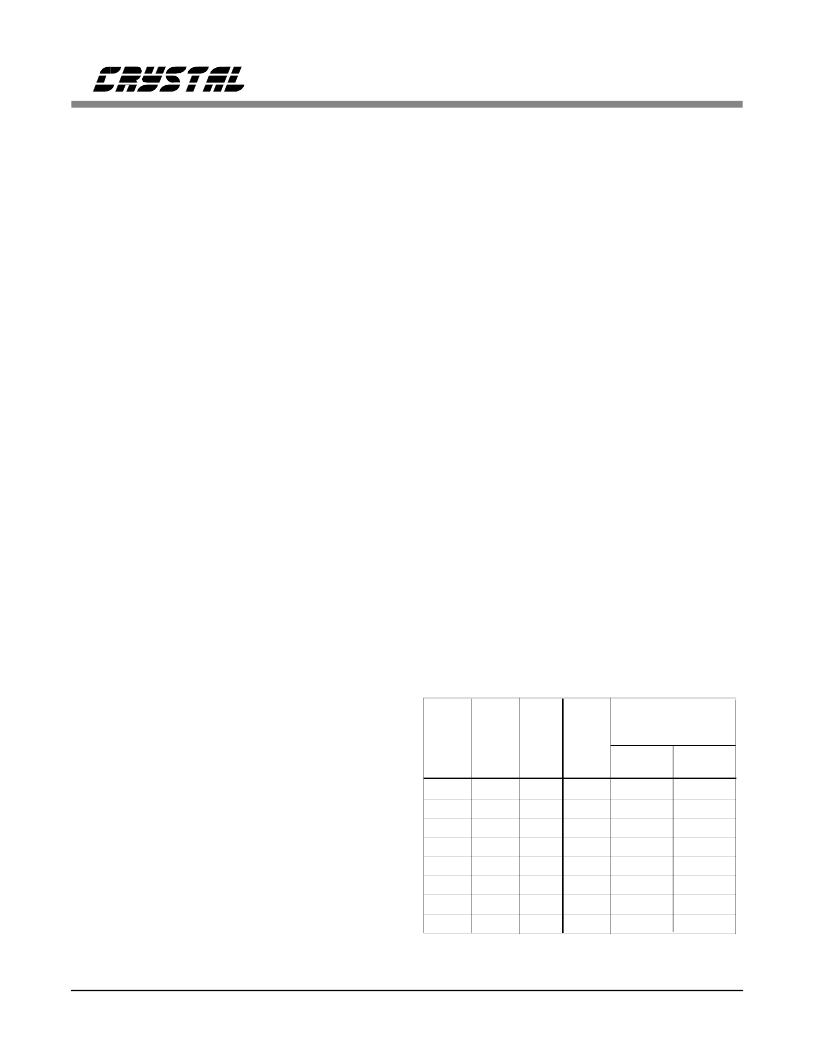

Sample Frequency Selection (Master

Sub-Modes)

In SM3-M and SM3-MM sub-modes, the multi-

function pins MF1:F1, MF2:F2, and MF3:F3 are

used to select the sample frequency divider. Ta-

ble 3 lists the decoding for the sample frequency

select pins where the sample frequency selected

is CLKIN/N. Also shown are the sample fre-

quencies obtained by using one of two example

master clocks: either 12.288 MHz or

11.2896 MHz. Changing sample frequency auto-

matically initiates a calibration cycle.

Fs (kHz)

with CLKIN

or 16xCLKIN

12.288

MHz

48.00

32.00

24.00

19.20

16.00

12.00

9.60

8.00

MF1:

MF2:

MF3:

N

F1

F2

F3

11.2896

MHz

44.10

29.40

22.05

17.64

14.70

11.025

8.82

7.35

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

256

384

512

640

768

1024

1280

1536

Table 3. SM3-M/SM3-MM/SM5, Fs Select

CS4218

18

DS135F1

相关PDF资料 |

PDF描述 |

|---|---|

| CS4218-KQ | 16-Bit Stereo Audio Codec |

| CS4218 | 16-Bit Stereo Audio Codec |

| CS4220 | 24-Bit Stereo Audio Codec with 3V Interface |

| CS4220-KS | IC EEPROM SRL 512X8BIT 8DIP |

| CS4221 | 24-Bit Stereo Audio Codec with 3V Interface |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4218-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4220 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit Stereo Audio Codec with 3V Interface |

| CS4220-KS | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit Stereo Audio Codec with 3V Interface |

| CS4220-KSR | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cirrus Logic 功能描述: |

| CS4220-KSZ | 功能描述:接口—CODEC IC 24Bit Str Audio CODEC 3V Intrfc RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。