参数资料

| 型号: | CS5530-ISZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 5/36页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT 1CH W/LNA 20-SSOP |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 3.84k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 45mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个差分,单极;1 个差分,双极 |

| 配用: | 598-1158-ND - BOARD EVAL FOR CS5530 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

CS5530

DS742F3

13

initialization sequence, the user must also perform

a system reset sequence which is as follows: Write

a logic 1 into the RS bit of the configuration regis-

ter. This will reset the calibration registers and

other logic (but not the serial port). A valid reset

will set the RV bit in the configuration register to a

logic 1. After writing the RS bit to a logic 1, wait

8 master clock cycles, then write the RS bit back to

logic 0. Note that the other bits in the configura-

tion register cannot be written on this write cycle

as they are being held in reset until RS is set back

to logic 0. While this involves writing an entire

word into the configuration register to casue the

RS bit to go to logic 0, the RV bit is a read only bit,

therefore a write to the configuration register will

not overwrite the RV bit. After clearing the RS bit

back to logic 0, read the configuration register to

check the state of the RV bit as this indicates that a

valid reset occurred. Reading the configuration

register clears the RV bit back to logic 0.

Completing the reset cycle initializes the on-chip

registers to the following states:

After the configuration register has been read to

clear the RV bit, the register can then be written to

set the other function bits or other registers can be

written or read.

Once the system initialization or reset is complet-

ed, the on-chip controller is initialized into com-

mand mode where it waits for a valid command

(the first 8-bits written into the serial port are shift-

ed into the command register). Once a valid com-

mand is received and decoded, the byte instructs

the converter to either acquire data from or transfer

data to an internal register, or perform a conversion

or a calibration. The Command Register Descrip-

tions section lists all valid commands.

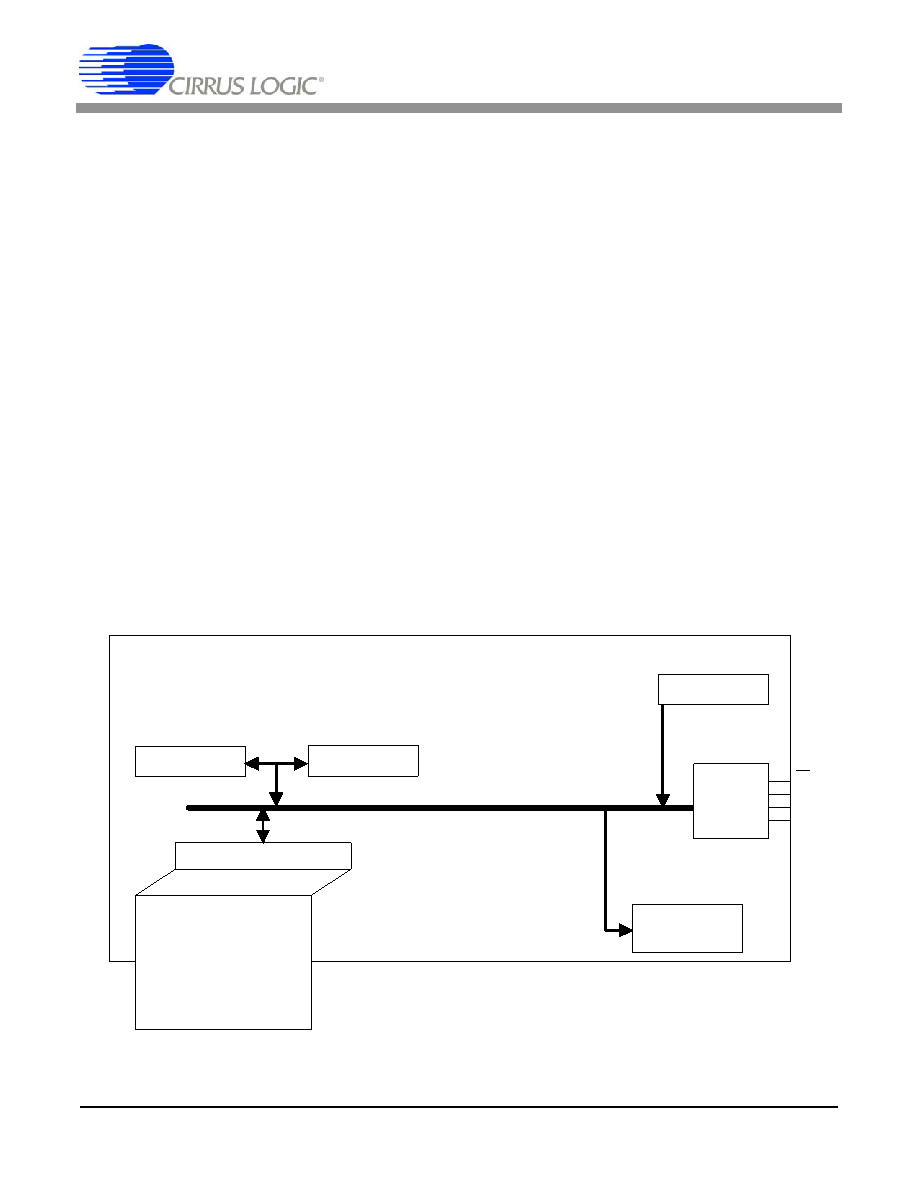

Offset (1 x 32)

Offset Register (1 x 32)

Conversion Data

Register (1 x 32)

Configuration Register (1 x 32)

Power Save Select

Reset System

Input Short

Voltage Reference Select

Output Latch

CS

SDI

SDO

SCLK

Read

On

ly

Command

Register (1 × 8)

Wr

it

e

O

n

ly

Serial

Interface

Data (1 x 32)

Filter Rate Select

Word Rate

Unipolar/Bipolar

Open Circuit Detect

Gain

(1 x 32)

Gain Register (1 x 32)

Figure 6. CS5530 Register Diagram

Configuration Register:

00000000(H)

Offset Register:

00000000(H)

Gain Register

01000000(H)

相关PDF资料 |

PDF描述 |

|---|---|

| CS5534-ASZR | IC ADC 24BIT 4CH W/LNA 24-SSOP |

| CS5534-BSZR | IC ADC 24BIT 4CH W/LNA 24SSOP |

| CS5550-ISZR | IC ADC 2CH LOW-COST 24-SSOP |

| CS5565-ISZ | IC ADC DELTA-SIGMA 24BIT 24-SSOP |

| CY28317PVXC-2 | IC CLK FTG VIA PL/E133T 48SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5531 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16 BIT AND 24 BIT ADCS WITH ULTRA LOW NOISE PGIA |

| CS5531_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-bit and 24-bit ADCs with Ultra-low-noise PGIA |

| CS5531-AS | 功能描述:模数转换器 - ADC 2-Ch 16-Bit ADCs w/ Ultra Low Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5531-ASR | 功能描述:模数转换器 - ADC IC 16-Bit ADCs w/UltraLw Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5531-ASZ | 功能描述:模数转换器 - ADC 2-Ch 16-Bit ADCs w/ Ultra Low Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。