参数资料

| 型号: | CS8420-DSZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 25/94页 |

| 文件大小: | 0K |

| 描述: | IC CONV S/R DGTL AUDIO 28-SOIC |

| 标准包装: | 27 |

| 类型: | 采样率转换器 |

| 应用: | 数字音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC |

| 包装: | 管件 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 其它名称: | 598-1729 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页

DS245F4

31

CS8420

9.2

IC Mode

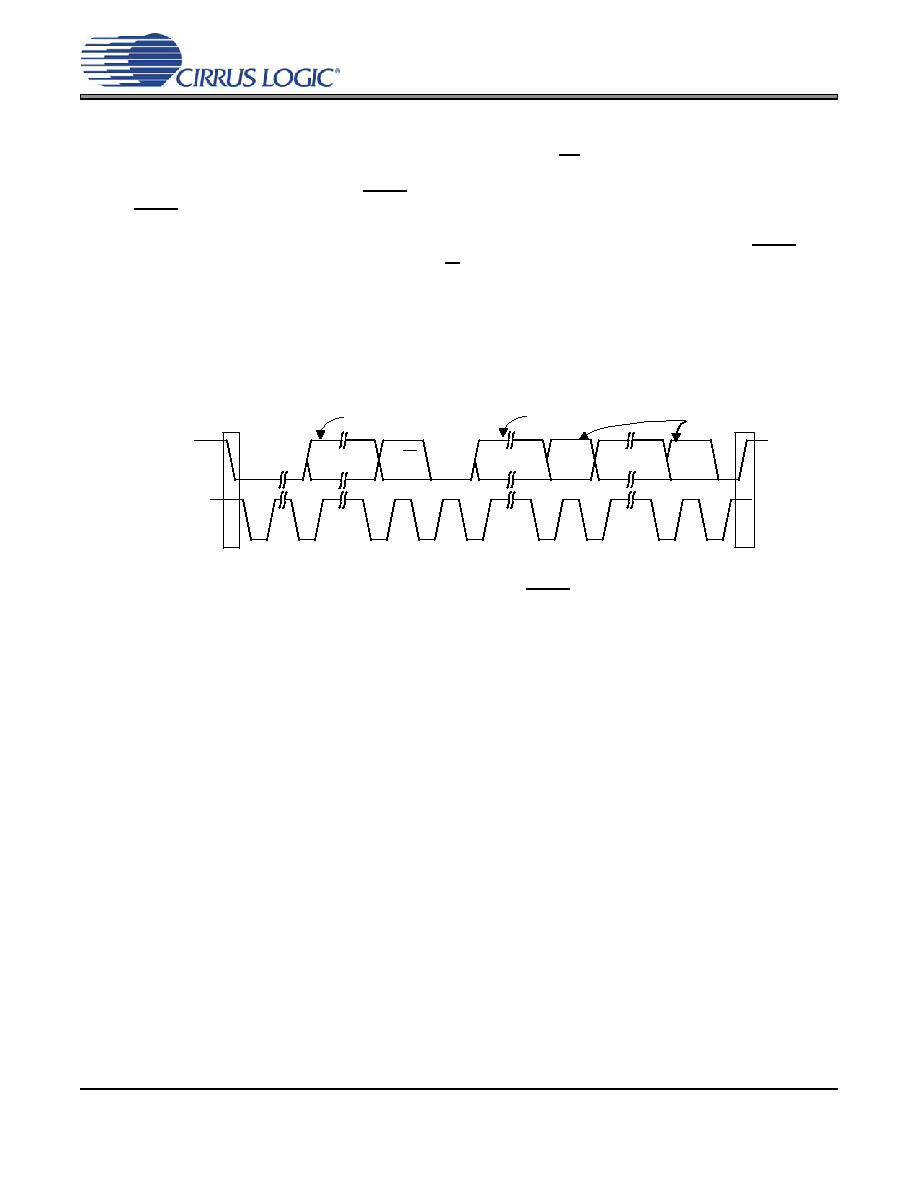

In IC mode, SDA is a bidirectional data line. Data is clocked into and out of the part by the clock, SCL, with

the clock to data relationship as shown in Figure 23. There is no CS pin. Each individual CS8420 is given a

unique address. Pins AD[1:0] form the two least significant bits of the chip address and should be connected

to VD+ or DGND as desired. The EMPH pin is used to set the AD2 bit, by connecting a resistor from the

EMPH pin to VD+ or to DGND. The state of the pin is sensed while the CS8420 is being reset. The upper

four bits of the 7-bit address field are fixed at 0010b. To communicate with a CS8420, the chip address field,

which is the first byte sent to the CS8420, should match 0010b followed by the settings of the EMPH, AD1,

and AD0. The eighth bit of the address is the R/W bit. If the operation is a write, the next byte is the Memory

Address Pointer (MAP) which selects the register to be read or written. If the operation is a read, the con-

tents of the register pointed to by the MAP will be output. Setting the auto-increment bit in MAP allows suc-

cessive reads or writes of consecutive registers. Each byte is separated by an acknowledge bit. The ACK

bit is output from the CS8420 after each input byte is read and is input to the CS8420 from the microcon-

troller after each transmitted byte.

9.3

Interrupts

The CS8420 has a comprehensive interrupt capability. The INT output pin is intended to drive the interrupt

input pin on the host microcontroller. The INT pin may be set to be active-low, active-high, or active-low with

no active pull-up transistor. This last mode is used for active-low, wired-OR hook-ups, with multiple periph-

erals connected to the microcontroller interrupt input pin.

Many conditions can cause an interrupt, as listed in the interrupt status register descriptions. Each source

may be masked via mask registers. In addition, each source may be set to rising-edge, falling-edge, or level-

sensitive. Combined with the option of level-sensitive or edge-sensitive modes within the microcontroller,

many different set-ups are possible, depending on the needs of the equipment designer.

SDA

SCL

0010

AD2-0

R/W

Start

ACK

DATA7-0

ACK

DATA7-0

ACK

Stop

Note 2

Note 1

Note 3

Figure 23. Control Port Timing in

IC Mode

1.

AD2 is derived from a resistor attached to the EMPH pin

AD1, and AD0 are determined by the state of the corresponding pins.

2.

If operation is a write, this byte contains the Memory Address Pointer, MAP.

3.

If operation is a read, the last bit of the read should be NACK (high).

Notes:

相关PDF资料 |

PDF描述 |

|---|---|

| CS8421-CNZ | IC SAMPLE RATE CONVERTER 20QFN |

| CS8427-DZZ | IC TXRX DGTL AUDIO 96KHZ 28TSSOP |

| CY28329ZXC | IC CLOCK CK408B PLUMAS 56SSOP |

| CY28346OXC | IC CLOCK DIFF OUT CK408 56SSOP |

| CY28346ZI-2 | IC CLOCK DIFF OUT CK408 56TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS8420-DSZR | 功能描述:音频 DSP IC Digital Audio Sample Rate Convertr RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| CS8421 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit, 192-kHz Asynchronous Sample Rate Converter |

| CS8421_06 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit, 192 kHz Asynchronous Sample Rate Converter |

| CS8421_09 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit, 192 kHz Asynchronous Sample Rate Converter |

| CS8421_10 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit, 192-kHz Asynchronous Sample Rate Converter |

发布紧急采购,3分钟左右您将得到回复。