- 您现在的位置:买卖IC网 > PDF目录256924 > CY38015V208-83NI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 15 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY38015V208-83NI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 15 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 2/32页 |

| 文件大小: | 929K |

| 代理商: | CY38015V208-83NI |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

PRELIMINARY

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. **

Page 10 of 32

Timing Model

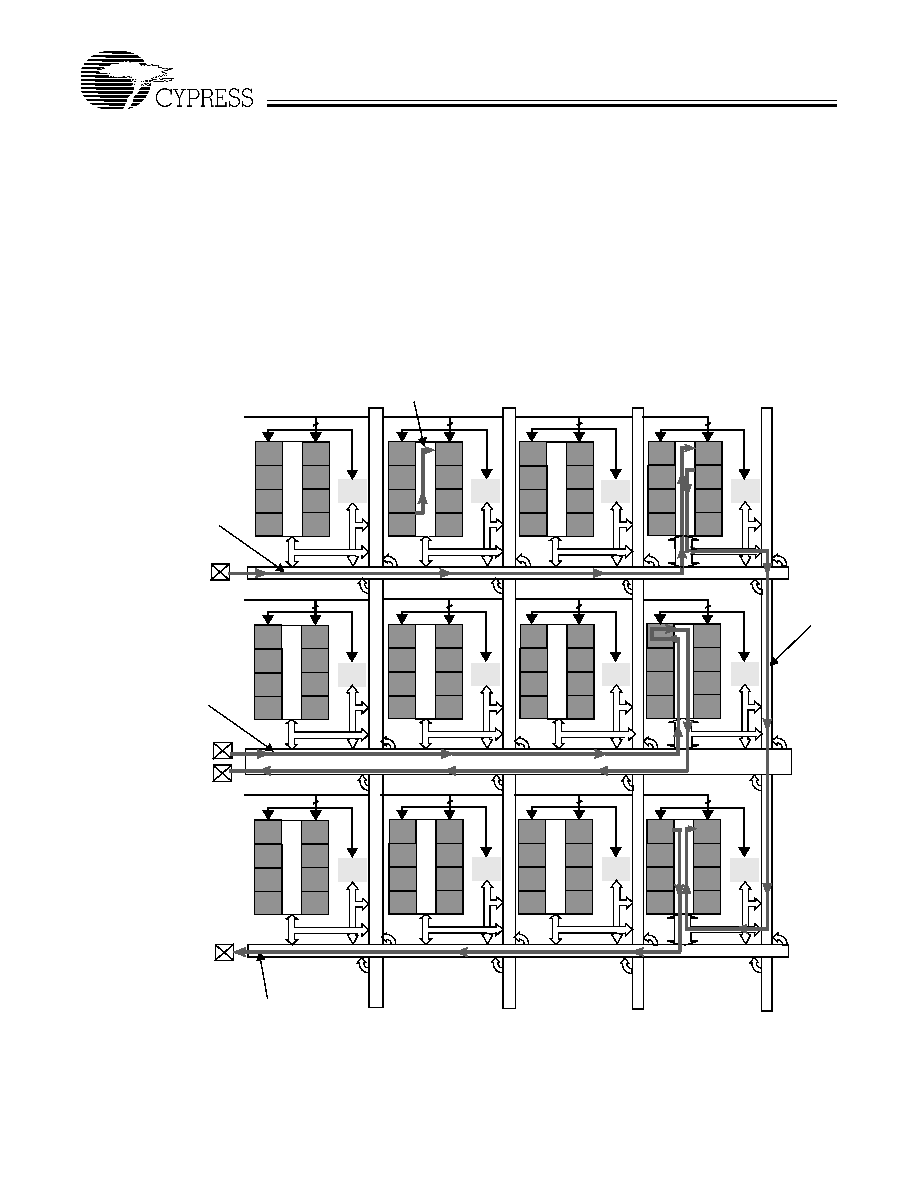

One important feature of the Quantum38K family is the sim-

plicity of its timing. All combinatorial and registered/synchro-

nous delays are worst case and system performance is static

(as shown in the AC specs section) as long as data is routed

through the same horizontal and vertical channels. Figure 8

illustrates the true timing model for the 38K100 devices. For

synchronous clocking of macrocells, a delay is incurred from

macrocell clock to macrocell clock of separate Logic Blocks

within the same cluster, as well as separate Logic Blocks with-

in different clusters. This is respectively shown as tSCS and

output (from corner to corner on the device), incurs a worst-

case delay in the 38K100 regardless of the amount of logic or

which horizontal and vertical channels are used. This is the tPD

shown in Figure 8. For synchronous systems, the input set-up

time to the output macrocell register and the clock to output

time are shown as the parameters tMCS and tMCCO shown in

the Figure 8. These measurements are for any output and syn-

chronous clock, regardless of the logic placement.

The Quantum38K features:

no dedicated vs. I/O pin delays

no penalty for using 0–16 product terms

no added delay for steering product terms

no added delay for sharing product terms

no output bypass delays

The simple timing model of the Quantum38K family eliminates

unexpected performance penalties.

Figure 8. Timing Model for 38K100 Device

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

Channel

RAM

4

GCLK[3:0]

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Channel

RAM

4

Channel

RAM

4

Channel

RAM

4

Channel

RAM

4

GCLK[3:0]

4

Channel

RAM

4

Channel

RAM

4

GCLK[3:0]

Channel

RAM

4

Channel

RAM

4

Channel

RAM

4

Channel

RAM

Channel

RAM

tMCS

tPD

tSCS

tMCCO

tSCS2

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

LB 0

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

PIM

相关PDF资料 |

PDF描述 |

|---|---|

| CY38015V256-66BBC | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38015V256-66BBI | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38015V256-83BBC | LOADABLE PLD, 15 ns, PBGA256 |

| CY38015V256-83BBI | LOADABLE PLD, 15 ns, PBGA256 |

| CP21600CPGA383A-0C | FPGA, 2940 CLBS, 13700 GATES, CPGA383 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

发布紧急采购,3分钟左右您将得到回复。