- 您现在的位置:买卖IC网 > PDF目录256924 > CY38015V208-83NI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 15 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY38015V208-83NI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 15 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 21/32页 |

| 文件大小: | 929K |

| 代理商: | CY38015V208-83NI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

PRELIMINARY

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. **

Page 28 of 32

Quantum38K100 Revisions/Errata

Two revisions of Quantum38K100 are currently offered which

are

marked

as

CY38100Vxxx

and

CY38100VxxxB.

CY38100VxxxB devices operate exactly as specified in this

datasheet. Following is the operation of the CY38100Vxxx

parts:

1. The internal regulator takes several seconds to power

down. Hence, cycling the power supply (within 8 seconds)

may cause a high standby current (200 mA to 1A) until the

part is configured.

2. The part always configures on power-up and will reconfig-

ure on HIGH to LOW edge of the Reconfig pin. Please refer

to the application note titled “Configuring

Delta39K/Quantum38K” for more details at

http://www.cypress.com.

3. The Self Config instruction starts reconfiguring the CPLD

upon execution of the Update-IR state of the JTAG TAP

controller state machine. In CY38100VxxxB parts, Self

Config instruction is executed upon execution of Test-Log-

ic-Reset state of the TAP controller.

4. An ESD failure is very unlikely. CDM ESD passes 1000V.

HBM ESD passes 3300V with all I/O bank’s VCCIO shorted

together. If VCCIOs in a bank are tested separately a per-

centage of parts will fail HBM ESD over 500V.

NoBL, PIM, Spread Aware, Warp, AnyVolt, Self-Boot, In-System Reprogrammable, ISR, and Quantum38K are trademarks of Cypress Semicon-

ductor Corporation.

ZBT is a trademark of IDT. QDR is a trademark of Micron, IDT, and Cypress Semiconductor Corporation.

SpeedWave, and ViewDraw are trademarks of ViewLogic.

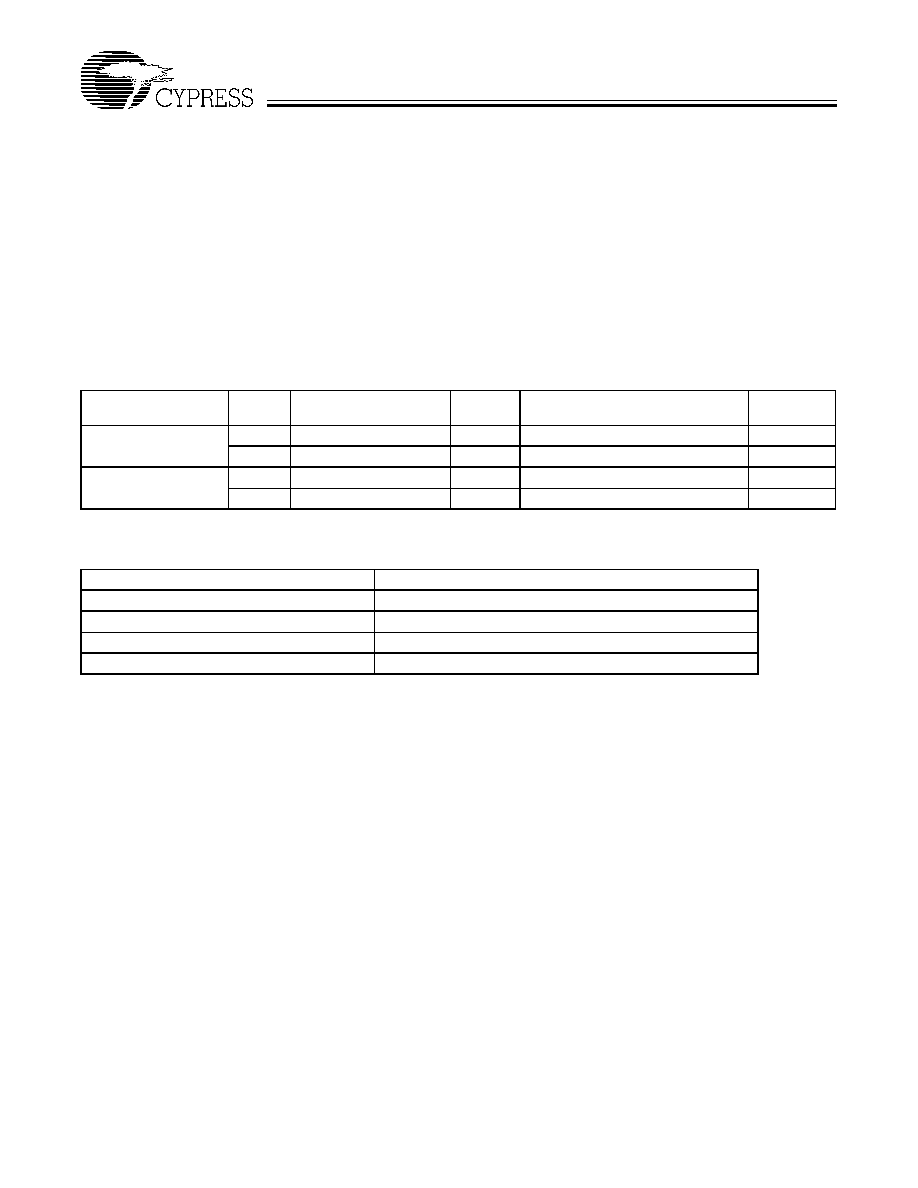

CPLD Boot EEPROM [10] Part Numbers (Ordering Information)

CPLD Boot EEPROM

Density

Speed

(MHz)

Ordering Code

Package

Name

Package Type

Operating

Range

1Mbit

15

CY3LV010-10JC

20J

20-Lead Plastic Leaded Chip Carrier

Commercial

10

CY3LV010-10JI

20J

20-Lead Plastic Leaded Chip Carrier

Industrial

512Kbit

15

CY3LV512-10JC

20J

20-Lead Plastic Leaded Chip Carrier

Commercial

10

CY3LV512-10JI

20J

20-Lead Plastic Leaded Chip Carrier

Industrial

Recommended CPLD Boot EEPROM for Corresponding Quantum38K CPLDs

CPLD Device

Recommended Boot EEPROM

38K15

CY3LV256

38K30

CY3LV512

38K50

CY3LV512

38K100

CY3LV010

Note:

10. See the data sheet titled “CPLD Boot EEPROM” for detailed architectural and timing information.

相关PDF资料 |

PDF描述 |

|---|---|

| CY38015V256-66BBC | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38015V256-66BBI | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38015V256-83BBC | LOADABLE PLD, 15 ns, PBGA256 |

| CY38015V256-83BBI | LOADABLE PLD, 15 ns, PBGA256 |

| CP21600CPGA383A-0C | FPGA, 2940 CLBS, 13700 GATES, CPGA383 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

发布紧急采购,3分钟左右您将得到回复。