- 您现在的位置:买卖IC网 > PDF目录256924 > CY38015V208-83NI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 15 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY38015V208-83NI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 15 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 30/32页 |

| 文件大小: | 929K |

| 代理商: | CY38015V208-83NI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页

PRELIMINARY

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. **

Page 7 of 32

Embedded Memory

The Quantum38K architecture includes an embedded channel

memory block at each crossing point of horizontal and vertical

routing channels. The channel memory is a 4096-bit memory

block that can be configured as asynchronous or synchronous

Single-Port RAM, Dual-Port RAM, or Read-Only memory

(ROM). The memory organization is configurable as 4Kx1,

2Kx2,1Kx4 or 512x8.

Data, address, and control inputs to the channel memory are

driven from horizontal and vertical routing channels. All data

logic outputs drive dedicated tracks in the horizontal and ver-

tical routing channels. The clocks for the channel memory

block are selected from four global clocks and pin inputs from

the horizontal and vertical channels. The clock muxes also

include a polarity mux for each clock so that the user can

choose an inverted clock.

Dual-Port (Channel Memory) Configuration

Each port has distinct address inputs, as well as separate data

and control inputs that can be accessed simultaneously. The

inputs to the Dual-Port memory are driven from the horizontal

and vertical routing channels. The data outputs drive dedicat-

ed tracks in the routing channels. The interface to the routing

is such that Port A of the Dual-Port interfaces primarily with the

horizontal routing channel and Port B interfaces primarily with

the vertical routing channel.

.

The clocks for each port of the Dual-Port configuration are

selected from four global clocks and two local clocks. One lo-

cal clock is sourced from the horizontal channel and the other

from the vertical channel. The data outputs of the dual-port

memory can also be registered. Clocks for the output registers

are also selected from four global clocks and two local clocks.

One clock polarity mux per port allows the use of true or com-

plement polarity for input and output clocking purposes.

Arbitration

The Dual-Port configuration of the Channel Memory Block pro-

vides arbitration when both ports access the same address at

the same time. Depending on the memory operations being

attempted, one port always gets priority. See Table 1 for details

on which port gets priority for read and write operations. An

active-LOW ‘Address Match’ signal is generated when an ad-

dress collision occurs.

Channel Memory Initialization

The channel memory powers up in an undefined state, but is

set to a user-defined known state during configuration. To fa-

cilitate the use of look-up-table (LUT) logic and ROM applica-

tions, the channel memory blocks can be initialized with a giv-

en set of data when the device is configured at power up. For

LUT and ROM applications, the user cannot write to memory

blocks.

Table 1. Arbitration Result: Address Match Signal

Becomes Active

Port A

Port B

Result of

Arbitration

Comment

Read

No arbitration

required

Both ports read at the

same time

Write

Read

Port A gets

priority

If Port B requests first

then it will read the cur-

rent data. The output will

then change to the newly

written data by Port A

Read

Write

Port B gets

priority

If Port A requests first

then it will read the cur-

rent data. The output will

then change to the newly

written data by Port B

Write

Port A gets

priority

Port B is blocked until

Port A is finished writing

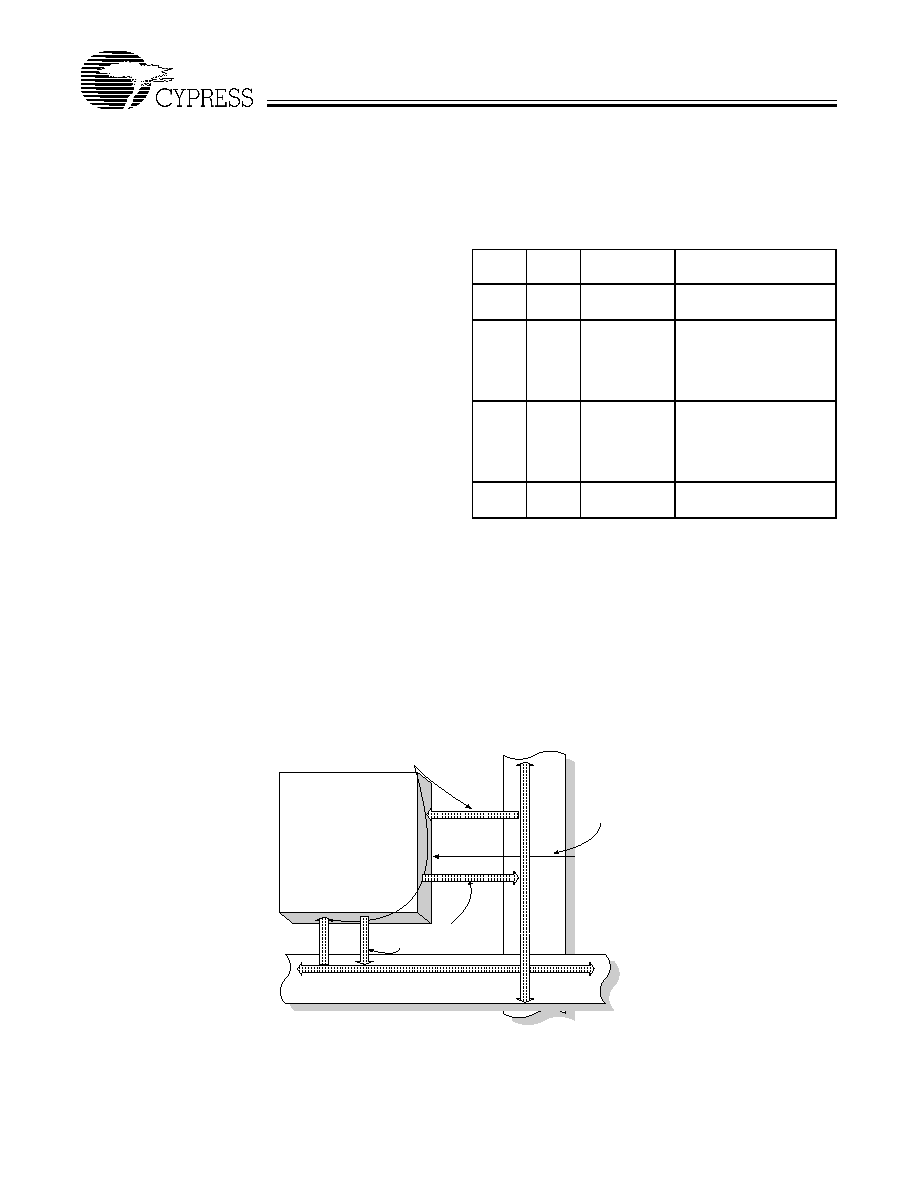

Figure 5. Block Diagram of Channel Memory Block

4096-bit Dual Port

Array

Configurable as

Async/Sync Dual Port

Configurable as

4Kx1, 2Kx2, 1Kx4 and

512x8 block sizes

Horizontal Channel

All channel memory

inputs are driven from

the routing channels

All channel memory outputs

drive dedicated tracks in the

routing channels

GCLK[3:0]

Global Clock

Signals

Ver

tic

al

C

hannel

相关PDF资料 |

PDF描述 |

|---|---|

| CY38015V256-66BBC | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38015V256-66BBI | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38015V256-83BBC | LOADABLE PLD, 15 ns, PBGA256 |

| CY38015V256-83BBI | LOADABLE PLD, 15 ns, PBGA256 |

| CP21600CPGA383A-0C | FPGA, 2940 CLBS, 13700 GATES, CPGA383 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

发布紧急采购,3分钟左右您将得到回复。