- 您现在的位置:买卖IC网 > PDF目录223638 > CY7C341B-25RI (CYPRESS SEMICONDUCTOR CORP) UV PLD, 40 ns, CPGA84 PDF资料下载

参数资料

| 型号: | CY7C341B-25RI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | UV PLD, 40 ns, CPGA84 |

| 封装: | WINDOWED, PGA-84 |

| 文件页数: | 10/12页 |

| 文件大小: | 339K |

| 代理商: | CY7C341B-25RI |

USE ULTRA37000 FOR

ALL NEW DESIGNS

CY7C341B

Document #: 38-03016 Rev. *C

Page 7 of 12

tFD

Feedback Delay

Commercial

1

2

ns

tPRE

Asynchronous Register Preset Time

Commercial

5

7

ns

tCLR

Asynchronous Register Clear Time

Commercial

5

7

ns

tPIA

Programmable Interconnect Array Delay Commercial

14

20

ns

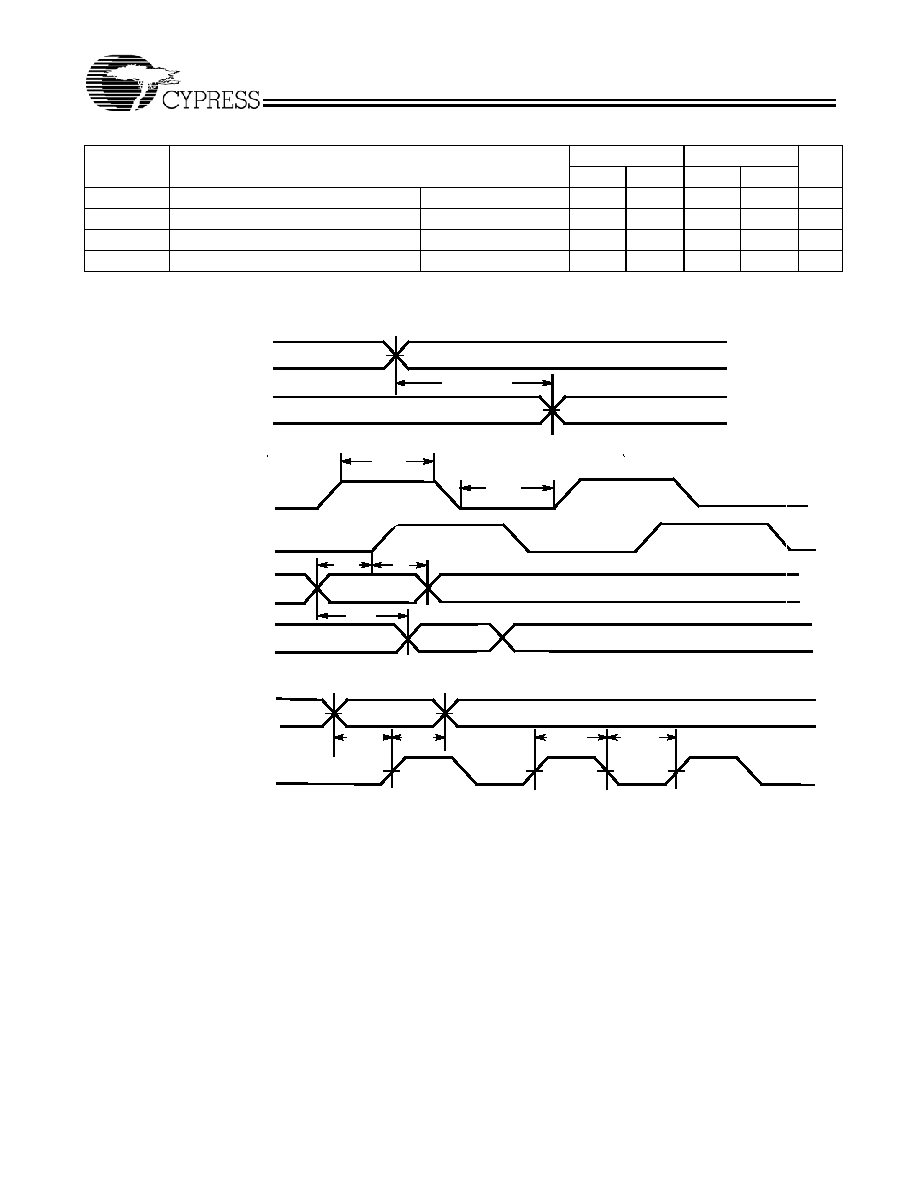

Internal Switching Characteristics Over the Operating Range (continued)

Parameter

Description

7C341B-25

7C341B-35

Unit

Min.

Max

Min.

Max

Switching Waveforms

External Combinatorial

DEDICATED INPUT/

I/O INPUT

COMBINATORIAL

OUTPUT

tPD1/tPD2

tWL

tSU

tH

tWH

External Synchronous

CLOCK AT REGISTER

SYNCHRONOUS

LOGIC ARRAY

DATA FROM

REGISTERED

CLOCK PIN

OUTPUTS

tCO1

External Asynchronous

tAH

tAS1

tAWH

tAWL

DEDICATED INPUTS OR

REGISTERED FEEDBACK

ASYNCHRONOUS

CLOCK INPUT

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C341B-35RC | UV PLD, 55 ns, CPGA84 |

| CY7C341B-35RI | UV PLD, 55 ns, CPGA84 |

| CY7C341B-25HC | UV PLD, 40 ns, CQCC84 |

| CY7C341B-25HI | UV PLD, 40 ns, CQCC84 |

| CY7C341B-35HC | UV PLD, 55 ns, CQCC84 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C341B-35JI | 制造商:Cypress Semiconductor 功能描述:CPLD MAX 制造商:QP Semiconductor 功能描述:7C341B CYP DIE 35NS-PLCC |

| CY7C341B-35RI | 制造商:Cypress Semiconductor 功能描述:CPLD MAX? Family 3.75K Gates 192 Macro Cells 33.3MHz 0.65um Technology 5V 84-Pin Windowed PGA |

| CY7C342-25HC | 制造商:Cypress Semiconductor 功能描述:CMOS EPLD SMD 7C342 PLCC68 5V |

| CY7C342-30HC | 制造商:Cypress Semiconductor 功能描述: 制造商:Cypress Semiconductor 功能描述:Complex Erasable Programmable Logic Device, 128 Cell, 30ns, 68 Pin, Ceramic, PLCC |

| CY7C34235HMB | 制造商:CYPRESS 功能描述:New |

发布紧急采购,3分钟左右您将得到回复。