- 您现在的位置:买卖IC网 > PDF目录223638 > CY7C341B-25RI (CYPRESS SEMICONDUCTOR CORP) UV PLD, 40 ns, CPGA84 PDF资料下载

参数资料

| 型号: | CY7C341B-25RI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | UV PLD, 40 ns, CPGA84 |

| 封装: | WINDOWED, PGA-84 |

| 文件页数: | 6/12页 |

| 文件大小: | 339K |

| 代理商: | CY7C341B-25RI |

USE ULTRA37000 FOR

ALL NEW DESIGNS

CY7C341B

Document #: 38-03016 Rev. *C

Page 3 of 12

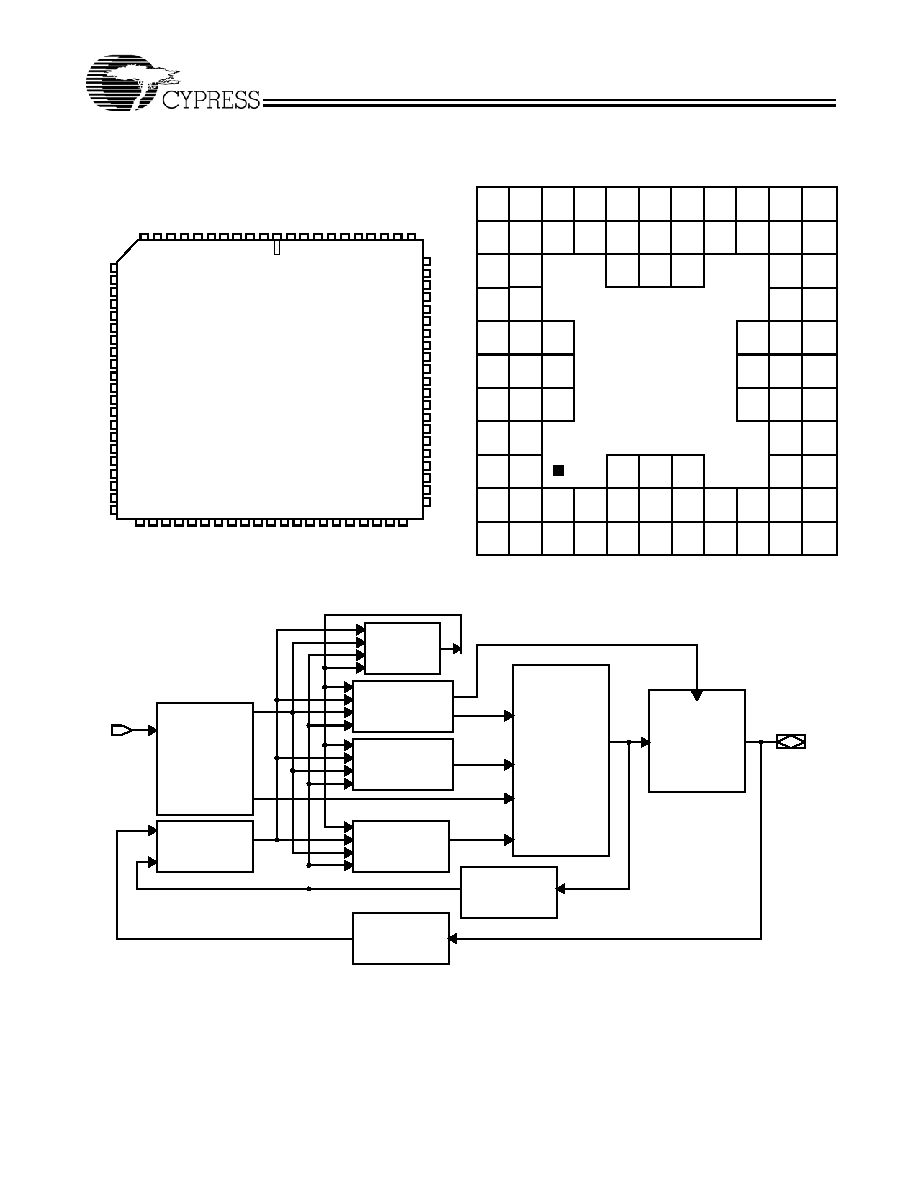

Pin Configurations

Figure 1. CY7C341B Internal Timing Model

I/O

Top View

PLCC/HLCC

9 8

6

7

5

13

14

12

11 10

49

48

58

59

60

23

24

26

25

27

15

16

47

46

43

28

33

20

21

19

18

17

22

34 35

37

36

38 39

42

41

43 44 45

40

66

65

63

64

62

61

V

CC

7C341B

67

68

69

74

72

73

71

70

84 83

81

82

80

21

79

I/O

INPUT

I/O

INPUT/CLK

INPUT

GND

I/O

GND

I/O

VCC

V

CC

INPUT

GND

INP

U

T

I/O

GND

I/O

VCC

I/O

VCC

INPUT

INPUT/

CLK

GND

I/O

VCC

I/O

GND

I/O

VCC

INPUT

I/O

GND

I/O

VCC

I/O

GND

I/O

PGA

Bottom View

7C341B

INPUT

GND

I/O

L

K

J

H

G

F

E

D

C

B

A

12

34

56

7

8

9

10

11

I/O

INPUT INPUT

INPUT

I/O

53

52

51

50

30

29

31

32

I/O

54

55

56

57

I/O

77

78

76 75

I/O

GND

INP

U

T

INP

U

T

GND

I/O

LOGIC ARRAY

CONTROL DELAY

tLAC

EXPANDER

DELAY

tEXP

CLOCK

DELAY

tIC

tRD

tCOMB

tLATCH

INPUT

DELAY

tIN

PIA

DELAY

tPIA

REGISTER

OUTPUT

DELAY

tOD

tXZ

tZX

LOGIC ARRAY

DELAY

tLAD

LOGIC ARRAY

DELAY

tFD

I/O DELAY

tIO

INPUT/

OUTPUT

INPUT

SYSTEM CLOCK DELAY tICS

tRH

tRSU

tPRE

tCLR

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C341B-35RC | UV PLD, 55 ns, CPGA84 |

| CY7C341B-35RI | UV PLD, 55 ns, CPGA84 |

| CY7C341B-25HC | UV PLD, 40 ns, CQCC84 |

| CY7C341B-25HI | UV PLD, 40 ns, CQCC84 |

| CY7C341B-35HC | UV PLD, 55 ns, CQCC84 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C341B-35JI | 制造商:Cypress Semiconductor 功能描述:CPLD MAX 制造商:QP Semiconductor 功能描述:7C341B CYP DIE 35NS-PLCC |

| CY7C341B-35RI | 制造商:Cypress Semiconductor 功能描述:CPLD MAX? Family 3.75K Gates 192 Macro Cells 33.3MHz 0.65um Technology 5V 84-Pin Windowed PGA |

| CY7C342-25HC | 制造商:Cypress Semiconductor 功能描述:CMOS EPLD SMD 7C342 PLCC68 5V |

| CY7C342-30HC | 制造商:Cypress Semiconductor 功能描述: 制造商:Cypress Semiconductor 功能描述:Complex Erasable Programmable Logic Device, 128 Cell, 30ns, 68 Pin, Ceramic, PLCC |

| CY7C34235HMB | 制造商:CYPRESS 功能描述:New |

发布紧急采购,3分钟左右您将得到回复。