- 您现在的位置:买卖IC网 > PDF目录381717 > DS1221 (DALLAS SEMICONDUCTOR) Nonvolatile Controller x 4 Chip(非易失性控制器x 4芯片) PDF资料下载

参数资料

| 型号: | DS1221 |

| 厂商: | DALLAS SEMICONDUCTOR |

| 元件分类: | 电源管理 |

| 英文描述: | Nonvolatile Controller x 4 Chip(非易失性控制器x 4芯片) |

| 中文描述: | 3-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDIP16 |

| 封装: | 0.300 INCH, DIP-16 |

| 文件页数: | 6/8页 |

| 文件大小: | 102K |

| 代理商: | DS1221 |

DS1221

072498 6/8

SECURITY OPTION

When activated by Dallas Semiconductor, the security

option prevents unauthorized access. A sequence of

events must occur to gain access to the memories (Fig-

ure 3). First, a dummy read cycle or a 200 ns active low

reset pulse is executed to initialize the sequence. Sec-

ond, a 64–bit access code must be consecutively writ-

ten to the DS1221 using the write enable signal (WE),

the chip enable signal (CE), and the data input/output

signal (DQ). The code is written to the DS1221 without

regard to the address. Actual RAM locations are not

written, as the security option is intercepting the data

path until access is granted. Instead, a special 64–bit

write only register is written. Following the 64 write

cycles, the register is compared to a 64–bit pattern

uniquely defined by the user and programmed into the

DS1221 by Dallas Semiconductor at the time of man-

ufacture. This pattern can only be interrogated by an in-

telligent controller within the DS1221 and cannot be

read by the user. If a read cycle occurs before 64 write

cycles are completed, the security sequence is aborted.

When a correct match for 64 bits is received, the third

part of the security sequence begins by reading a 64–bit

read only register. This register consists of 64 bits also

defined by the user and programmed into the DS1221

by Dallas Semiconductor at the time of manufacture.

For each of the 64 read cycles, one bit of the user–de-

fined read only register is driven onto the DQ line. This

phase also requires that the 64 read cycles be consecu-

tive. The data being read from the read only register can

be used by software to determine if the DS1221 will be

permitted to be used with that particular system. After

the 64th read cycle has been executed the DS1221 is

unlocked and all subsequent memory cycles will be

passed through and will become actual memory ac-

cesses based upon address inputs. If V

CC

falls below

4.5 volts or the reset line is driven low, the entire security

sequence must be executed again in order to access

memory locations.

NOTE:

Contact Dallas Semiconductor sales office for code as-

signments.

SECURITY OPTION

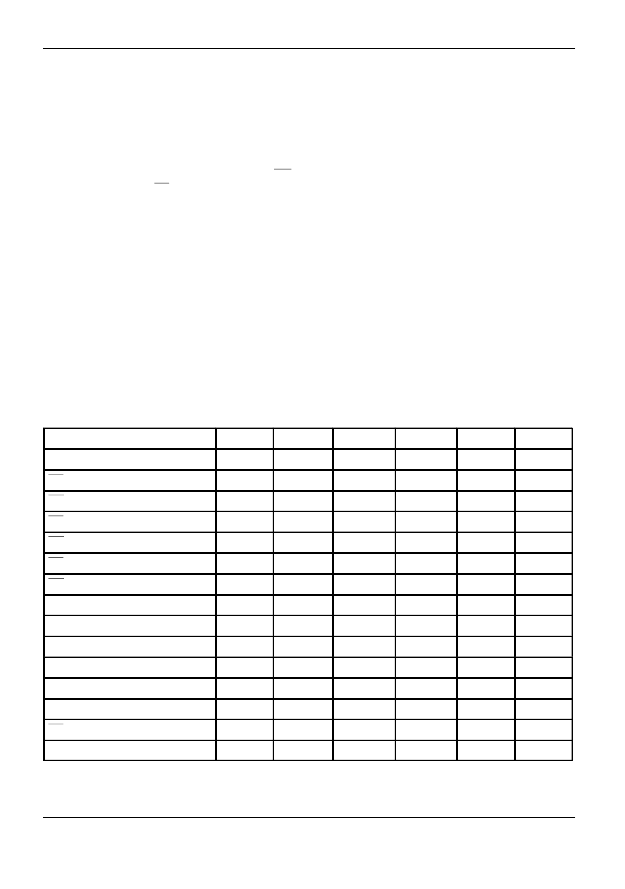

AC ELECTRICAL CHARACTERISTICS

(0

°

C to 70

°

C; V

CC

= 5V

±

10%)

MAX

UNITS

PARAMETER

SYMBOL

MIN

TYP

NOTES

Read Cycle Time

t

RC

250

ns

CE Access Time

t

CO

200

ns

RD Access Time

t

OE

100

ns

CE to Output Low Z

t

COE

10

ns

RD to Output Low Z

t

OEE

10

ns

CE to Output High Z

t

OD

100

ns

RD to Output High Z

t

ODO

100

ns

Read Recovery

t

RR

50

ns

Write Cycle

t

WC

250

ns

Write Pulse Width

t

WP

170

ns

Write Recovery

t

WR

50

ns

Data Setup

t

DS

100

ns

Data Hold Time

t

DH

0

ns

CE Pulse Width

t

CW

170

ns

Reset Pulse Width

t

RST

200

ns

相关PDF资料 |

PDF描述 |

|---|---|

| DS1222 | BankSwitch Chip(存储器组切换芯片) |

| DS1225AB | 64K Nonvolatile SRAM(64K非易失性静态RAM) |

| DS1225AD | 16K Nonvolatile SRAM(64K非易失性SRAM) |

| DS1225Y | 64K Nonvolatile SRAM(64K 非易失性静态RAM) |

| DS1230AB(中文) | 256K NV SRAM(256K非易失性SRAM) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1221S | 功能描述:IC CTRLR/DECODER 4BIT 16-SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 - 控制器 系列:- 标准包装:45 系列:- 控制器类型:静态 RAM(SRAM) 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC W 包装:管件 |

| DS1221S/T&R | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS1221S/T&R | 功能描述:NVRAM RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube |

| DS1221SN | 功能描述:IC CTRLR/DECODER 4BIT IN 16-SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 - 控制器 系列:- 标准包装:45 系列:- 控制器类型:静态 RAM(SRAM) 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC W 包装:管件 |

| DS1222 | 功能描述:IC BANKSWITCH CMOS 14-DIP RoHS:否 类别:集成电路 (IC) >> 存储器 - 控制器 系列:- 标准包装:45 系列:- 控制器类型:静态 RAM(SRAM) 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC W 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。