- 您现在的位置:买卖IC网 > PDF目录1914 > DS2172T/T&R (Maxim Integrated Products)IC TESTER BIT ERROR RATE 32-TQFP PDF资料下载

参数资料

| 型号: | DS2172T/T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 21/22页 |

| 文件大小: | 0K |

| 描述: | IC TESTER BIT ERROR RATE 32-TQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS |

| 产品变化通告: | Product Discontinuation 20/Feb/2012 |

| 标准包装: | 250 |

| 功能: | 位误码率测试器(BERT) |

| 接口: | T1 |

| 电路数: | 1 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 10mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 带卷 (TR) |

| 包括: | 错误计数器,样式发生器和检测器 |

DS2172

8 of 22

6.0 PATTERN CONTROL REGISTER

The Pattern Control Register (PCR) is used to configure the operating parameters of the DS2172 and to

control the patterns being generated and received. Also the PCR is used to control the pattern

synchronizer and the error and bit counters.

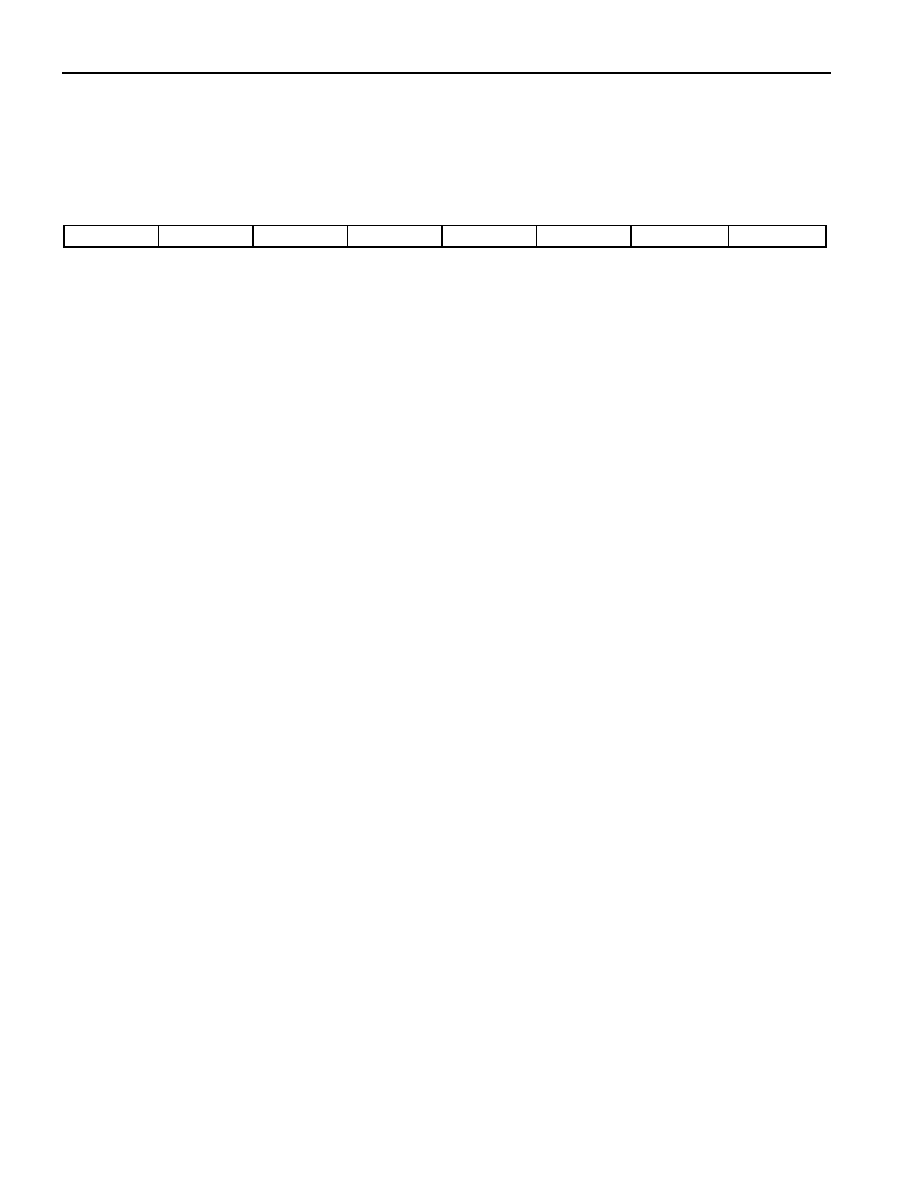

PCR: PATTERN CONTROL REGISTER (Address=06 Hex)

(MSB)

(LSB)

TL

QRSS

PS

LC

RL

SYNCE

RESYNC

LPBK

SYMBOL

POSITION

NAME AND DESCRIPTION

TL

PCR.7

Transmit Load. A low to high transition loads the pattern generator with

the contents of the Pattern Set Registers. PCR.7 is logically OR’ed with the

input pin TL. Must be cleared and set again for subsequent loads.

QRSS

PCR.6

Zero Suppression Select. Forces a 1 into the pattern whenever the next 14

bit positions are all 0s. Should only be set when using the QRSS pattern.

0 = Zero suppression disabled

1 = Zero suppression enabled

PS

PCR.5

Pattern Select.

0 = Repetitive Pattern

1 = Pseudorandom Pattern

LC

PCR.4

Latch Count Registers. A low to high transition latches the bit and error

counts into the user accessible registers BCR and BECR and clears the

internal register count. PCR.4 is logically OR’ed with input pin LC. Must

be cleared and set again for subsequent loads.

RL

PCR.3

Receive Data Load. A transition from low to high loads the previous

32 bits of data received at RDATA into the Pattern Receive Registers

(PRR). PCR.3 is logically OR’ed with input pin RL. Must be cleared and

set again for subsequent latches.

SYNCE

PCR.2

SYNC Enable.

0 = auto resync is enabled.

1 = auto resync is disabled.

RESYNC

PCR.1

Initiate Manual Resync Process. A low to high transition will force the

DS2172 to resynchronize to the incoming pattern at RDATA. Must be

cleared and set again for a subsequent resync.

LPBK

PCR.0

Transmit/Receive Loopback Select. When enabled, the RDATA input is

disabled; TDATA continues to output data as normal. See Figure 1.

0 = loopback disabled

1 = loopback enabled

相关PDF资料 |

PDF描述 |

|---|---|

| DS2174QN+ | IC BERT ENHANCED 44-PLCC |

| DS2175SN+ | IC ELASTIC STORE T1/CEPT 16-SOIC |

| DS2176QN | IC BUFFER RECEIVE T1 IND 28-PLCC |

| DS2180AQN+T&R | IC TRANSCEIVER T1 44-PLCC |

| DS2181AQN+ | IC TXRX CEPT PRIMARY RATE 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2174 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:EBERT |

| DS2174DK | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Enhanced Bit Error-Rate Tester Design Kit |

| DS2174Q | 功能描述:电信集成电路 Enhanced Bit Error Rate Tester (BERT) RoHS:否 制造商:STMicroelectronics 类型:Telecom IC - Various 工作电源电压:4.75 V to 5.25 V 电源电流: 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-100 封装:Tray |

| DS2174Q/T&R+ | 制造商:Maxim Integrated Products 功能描述:BIT ERROR RATE TESTER 44PLCC - Tape and Reel |

| DS2174Q/T&R | 功能描述:电信集成电路 RoHS:否 制造商:STMicroelectronics 类型:Telecom IC - Various 工作电源电压:4.75 V to 5.25 V 电源电流: 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-100 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。