- 您现在的位置:买卖IC网 > PDF目录1914 > DS2172T/T&R (Maxim Integrated Products)IC TESTER BIT ERROR RATE 32-TQFP PDF资料下载

参数资料

| 型号: | DS2172T/T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/22页 |

| 文件大小: | 0K |

| 描述: | IC TESTER BIT ERROR RATE 32-TQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS |

| 产品变化通告: | Product Discontinuation 20/Feb/2012 |

| 标准包装: | 250 |

| 功能: | 位误码率测试器(BERT) |

| 接口: | T1 |

| 电路数: | 1 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 10mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 带卷 (TR) |

| 包括: | 错误计数器,样式发生器和检测器 |

DS2172

12 of 22

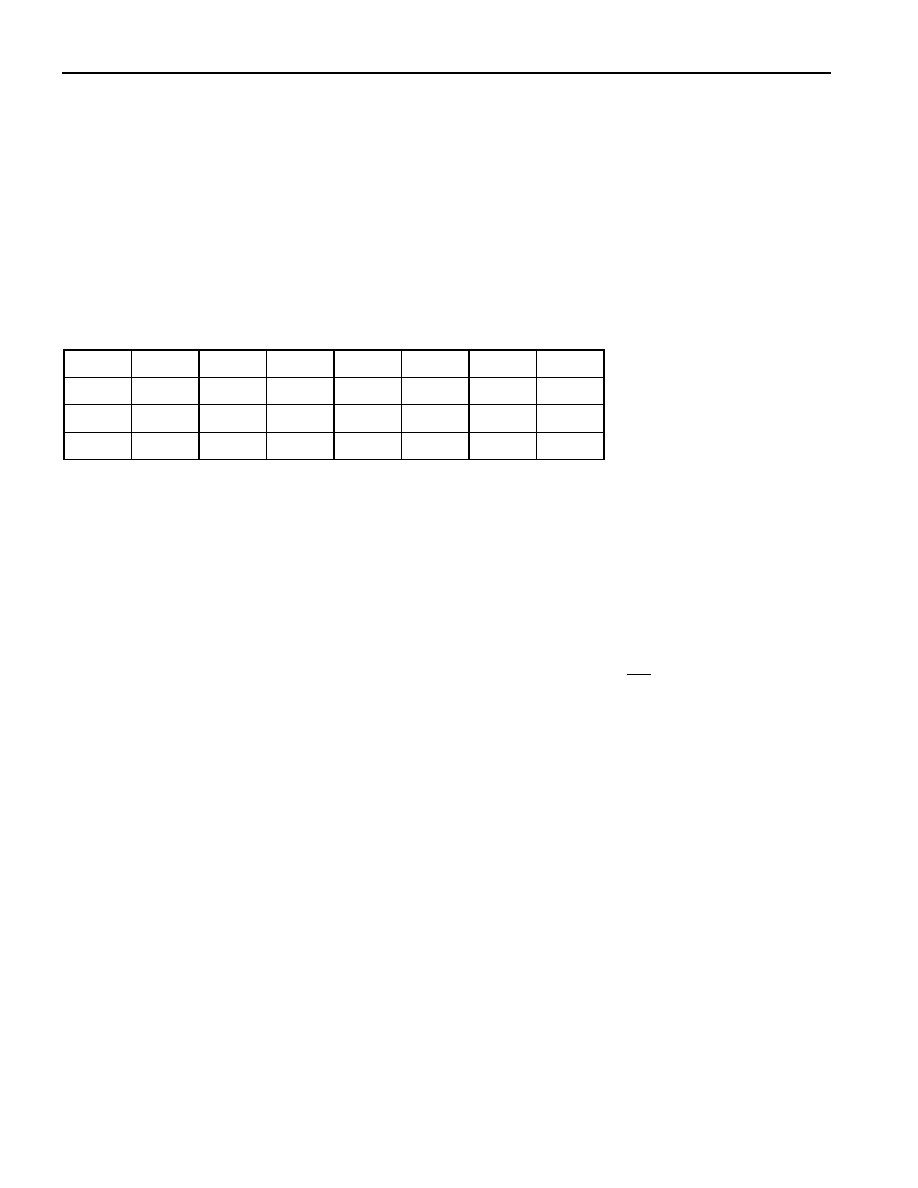

10.0 PATTERN RECEIVE REGISTERS

The Pattern Receive Register (PRR) provides access to the data patterns received at RDATA. The

operation of these registers depends on the synchronization status of the DS2172. Asserting the RL bit

(PCR.3) or pin during an out-of -sync condition (SR.0 = 0) will latch the previous 32 bits of data received

at RDATA into the PRR registers. When the DS2172 is in sync (SR.0 = 1) asserting RL will latch the

pattern that to which the device has established synchronization. Since the receiver has no knowledge of

the start or end of the pattern, the data in the PRR registers will have no particular alignment. As an

example, if the receiver has synchronized to the pattern 00100110, PRR1 may report 10011000,

11000100 or any rotation thereof. Once synchronization is established, bit errors cannot be viewed in the

PRR registers.

PATTERN RECEIVE REGISTERS

(MSB)

(LSB)

PR31

PR30

PR29

PR28

PR27

PR26

PR25

PR24

PRR3 (addr.=10 Hex)

PR23

PR22

PR21

PR20

PR19

PR18

PR17

PR16

PRR2 (addr.=11 Hex)

PR15

PR14

PR13

PR12

PR11

PR10

PR9

PR8

PRR1 (addr.=12 Hex)

PR7

PR6

PR5

PR4

PR3

PR2

PR1

PR0

PRR0 (addr.=13 Hex)

11.0 STATUS REGISTER AND INTERRUPT MASK REGISTER

The Status Register (SR) contains information on the current real time status of the DS2172. When a

particular event has occurred, the appropriate bit in the register will be set to a 1. All of the bits in these

registers (except for the SYNC bit) operate in a latched fashion. This means that if an event occurs and a

bit is set to a 1 in any of the registers, it will remain set until the user reads that bit. For the BED, BCOF,

and BECOF status bits, they will be cleared when read and will not be set again until the event has

occurred again. For RLOS, RA0, and RA1 status bits, they will be cleared when read if the condition no

longer persists.

The SR register has the unique ability to initiate a hardware interrupt via the INT pin. Each of the alarms

and events in the SR can be either masked or unmasked from the interrupt pins via the Interrupt Mask

Register (IMR).

相关PDF资料 |

PDF描述 |

|---|---|

| DS2174QN+ | IC BERT ENHANCED 44-PLCC |

| DS2175SN+ | IC ELASTIC STORE T1/CEPT 16-SOIC |

| DS2176QN | IC BUFFER RECEIVE T1 IND 28-PLCC |

| DS2180AQN+T&R | IC TRANSCEIVER T1 44-PLCC |

| DS2181AQN+ | IC TXRX CEPT PRIMARY RATE 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2174 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:EBERT |

| DS2174DK | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Enhanced Bit Error-Rate Tester Design Kit |

| DS2174Q | 功能描述:电信集成电路 Enhanced Bit Error Rate Tester (BERT) RoHS:否 制造商:STMicroelectronics 类型:Telecom IC - Various 工作电源电压:4.75 V to 5.25 V 电源电流: 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-100 封装:Tray |

| DS2174Q/T&R+ | 制造商:Maxim Integrated Products 功能描述:BIT ERROR RATE TESTER 44PLCC - Tape and Reel |

| DS2174Q/T&R | 功能描述:电信集成电路 RoHS:否 制造商:STMicroelectronics 类型:Telecom IC - Various 工作电源电压:4.75 V to 5.25 V 电源电流: 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-100 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。