- 您现在的位置:买卖IC网 > PDF目录3784 > DS87C550-QNL (Maxim Integrated Products)IC MCU EPROM ADC/PWM HS 68-PLCC PDF资料下载

参数资料

| 型号: | DS87C550-QNL |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 7/49页 |

| 文件大小: | 0K |

| 描述: | IC MCU EPROM ADC/PWM HS 68-PLCC |

| 标准包装: | 18 |

| 系列: | 87C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 33MHz |

| 连通性: | EBI/EMI,SIO,UART/USART |

| 外围设备: | 电源故障复位,PWM,WDT |

| 输入/输出数: | 55 |

| 程序存储器容量: | 8KB(8K x 8) |

| 程序存储器类型: | OTP |

| RAM 容量: | 1K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 4.5 V ~ 5.5 V |

| 数据转换器: | A/D 6x10b |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 68-LCC(J 形引线) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

DS87C550 EPROM High-Speed Microcontroller with ADC and PWM

15 of 49

cycles. It is important to note the distinction between the system clock and the machine cycle clock as

they are often confused, creating errors in timing calculations. In performing timing calculations, it is

important to remember that all timers and internal peripherals operate off of some version of the system

clock while the instruction execution engine always operates off of the machine cycle clock.

When CD1 and CD0 (PMR.7-6) are both cleared to a logic 0, the multiplexer selects the frequency

multiplier output. The frequency multiplier can supply a clock that is 2 times or 4 times the frequency of

the incoming signal. If the times-4 multiplier is selected by setting the 4X/ 2X bit (PMR.3) to 1, for

example, the incoming signal is multiplied by 4. This 4X clock is then passed through the multiplexer,

and then output to the CPU State Clock Generation circuits. These CPU State Clock Generation circuits

always divide the incoming clock by 4 to arrive at the four states (called a machine cycle) necessary for

correct processor operation. In this example, since the clock multiplier multiplies by four and the CPU

State Clock Generation circuit divides by 4, the apparent instruction execution speed is 1 external (or

crystal oscillator) clock per instruction. If the 4X/ 2X bit is set to 0, then the apparent instruction

execution speed is 2 clocks per instruction.

It is important to note that the clock multiplier function does not increase the maximum clock (system

clock) rate of the device. The DS87C550 operates at a maximum system clock rate of 33MHz. Therefore,

the maximum crystal frequency is 8.25MHz when a clock multiplier of 4 is used, and is 16.5MHz when a

clock multiplier of 2 is used. The purpose of the clock multiplier is to simplify crystal selection when

maximum processor operation is desired. Specifically, an 8.25MHz fundamental mode, AT cut, parallel

resonant crystal is much easier to obtain than the same crystal at 33MHz. Most crystals in that frequency

range tend to be third overtone type.

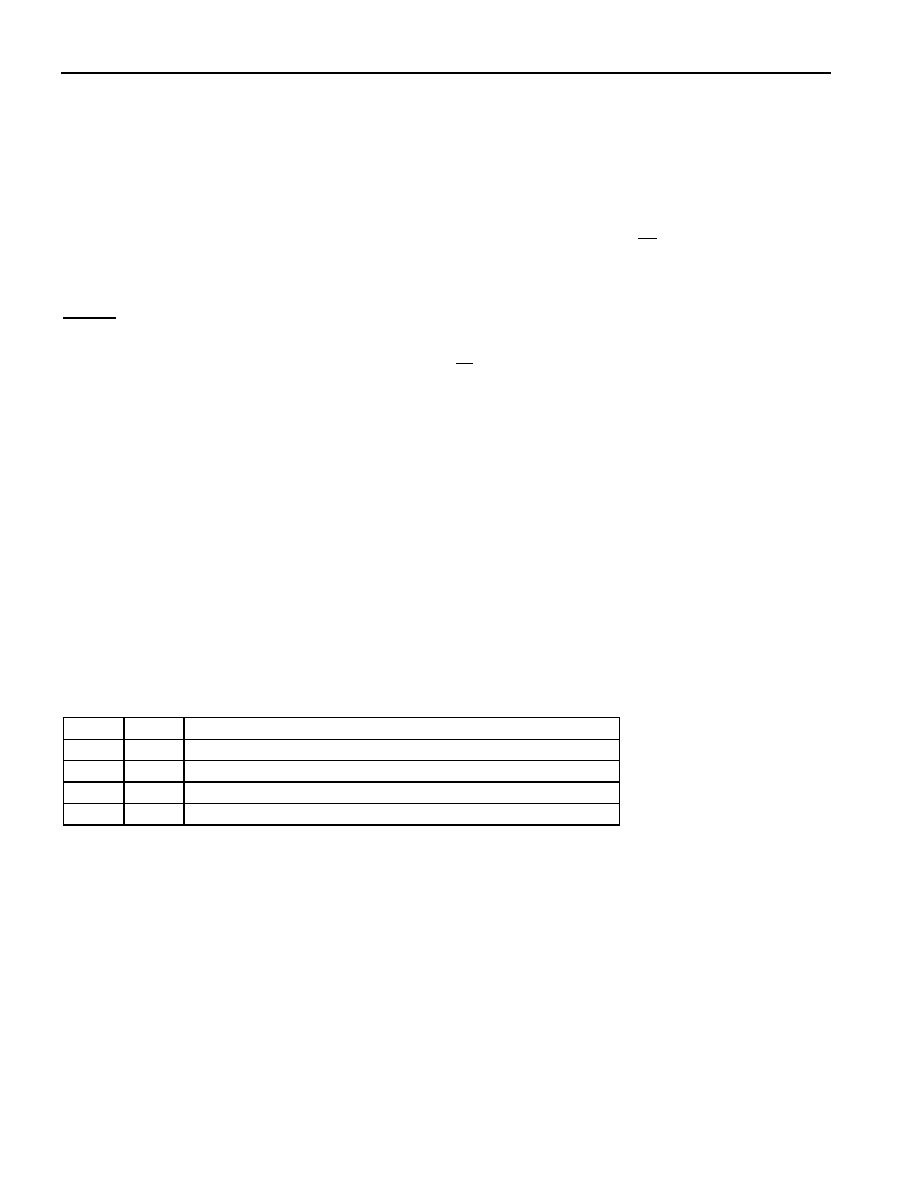

As illustrated in Figure 3, the programmable Clock Divide control bits CD1-CD0 (PMR.7-6) provide the

processor with the ability to adapt to different crystal (and external clock) frequencies and also to allow

extreme division of the incoming clock providing lower power operation when desired. The effect of

these bits is shown in Table 5.

CD1:CD0 OPERATION Table 5

CD1

CD0

Instruction Execution

0

Frequency multiplier (1 or 2 clocks per machine cycle)

0

1

Reserved

1

0

Clock divided by 4 (4 clocks per machine cycle) Default

1

Clock divided by 1024 (1024 clocks per machine cycle)

Besides the ability to use a multiplied clock signal, the normal mode of operation, i.e. the reset default

condition (CD1 = 1, CD0 = 0) passes the incoming crystal or external oscillator clock signal straight

through as the system clock. Because of the CPU State Clock generation circuitry’s normal divide-by-4

function, the default execution speed of the DS87C550’s basic instruction is one-fourth the clock

frequency.

The selection of instruction cycle rate takes effect after a delay of one machine cycle. Note that the clock

divider choice applies to all functions including timers. Since baud rates are altered, it may be difficult to

conduct serial communication while in divide-by-1024 mode. This is simplified by the use of switchback

mode (described later) included on the DS87C550.

相关PDF资料 |

PDF描述 |

|---|---|

| MC908LK24CPBE | IC MCU 8BIT 64-LQFP |

| 1588908-1 | JR FRRL KIT, PC 126 SEALED |

| 1278530-1 | RETAINING CLIP, 1X4 BACKPLANE |

| 1544551-1 | CONNECTOR 5V 6.35 |

| 492578-1 | DUST COVER,DAUGHTER CARD HSG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS88 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| DS8800 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Dual Voltage Level Translator |

| DS8800H | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Dual Voltage Level Translator |

| DS8800H/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TTL-to-MOS Translator |

| DS8802J/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MOS-to-TTL Translator |

发布紧急采购,3分钟左右您将得到回复。