参数资料

| 型号: | EFM32TG210F32 |

| 厂商: | Energy Micro |

| 文件页数: | 19/136页 |

| 文件大小: | 0K |

| 描述: | MCU 32BIT 32KB FLASH 32-QFN |

| 特色产品: | EFM32 Tiny Gecko |

| 标准包装: | 1 |

| 系列: | Tiny Gecko |

| 核心处理器: | ARM? Cortex?-M3 |

| 芯体尺寸: | 32-位 |

| 速度: | 32MHz |

| 连通性: | EBI/EMI,I²C,IrDA,智能卡,SPI,UART/USART |

| 外围设备: | 欠压检测/复位,DMA,POR,PWM,WDT |

| 输入/输出数: | 24 |

| 程序存储器容量: | 32KB(32K x 8) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 4K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 1.8 V ~ 3.8 V |

| 数据转换器: | A/D 4x12b,D/A 1x12b |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 32-VQFN 裸露焊盘 |

| 包装: | 标准包装 |

| 其它名称: | 914-1034-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页

...the world's most energy friendly microcontrollers

2011-02-04 - d0002_Rev1.00

115

www.energymicro.com

Reserved

31

24 23

16 15

8 7

1 0

IREGION

DREGION

Reserved

SEPARATE

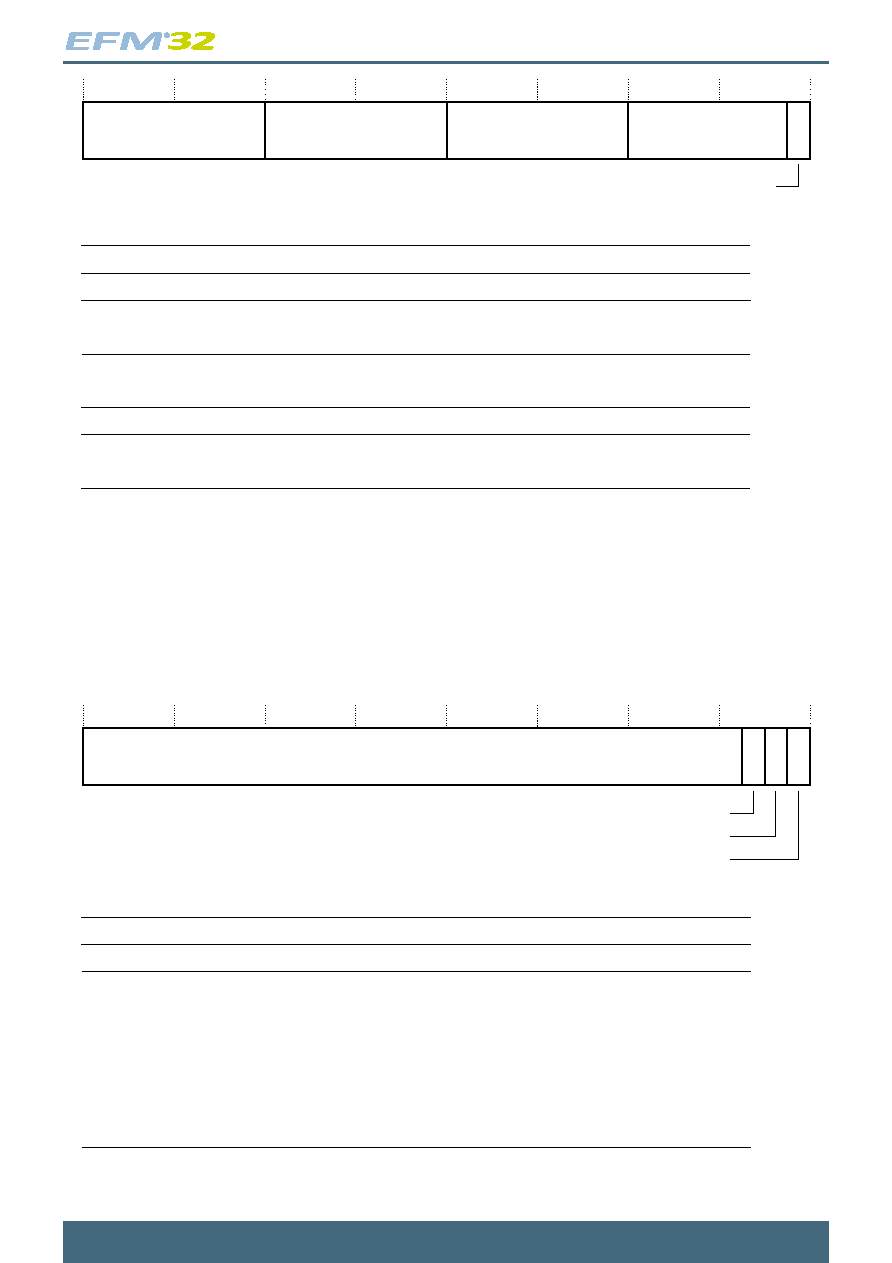

Table 4.39. TYPE register bit assignments

Bits

Name

Function

[31:24]

-

Reserved.

[23:16]

IREGION

Indicates the number of supported MPU instruction regions.

Always contains 0x00. The MPU memory map is unified and is described by the DREGION field.

[15:8]

DREGION

Indicates the number of supported MPU data regions:

0x08

= Eight MPU regions.

[7:0]

-

Reserved.

[0]

SEPARATE

Indicates support for unified or separate instruction and date memory maps:

0 = unified.

4.5.2 MPU Control Register

The MPU CTRL register:

enables the MPU

enables the default memory map background region

enables use of the MPU when in the hard fault, Non-maskable Interrupt (NMI), and FAULTMASK

escalated handlers.

See the register summary in Table 4.38 (p. 114) for the MPU CTRL attributes. The bit assignments are:

31

1 0

Reserved

HFNMIENA

ENABLE

2

PRIVDEFENA

3

Table 4.40. MPU CTRL register bit assignments

Bits

Name

Function

[31:3]

-

Reserved.

[2]

PRIVDEFENA

Enables privileged software access to the default memory map:

0 = If the MPU is enabled, disables use of the default memory map. Any memory access to a

location not covered by any enabled region causes a fault.

1 = If the MPU is enabled, enables use of the default memory map as a background region for

privileged software accesses.

When enabled, the background region acts as if it is region number -1. Any region that is

defined and enabled has priority over this default map.

If the MPU is disabled, the processor ignores this bit.

[1]

HFNMIENA

Enables the operation of MPU during hard fault, NMI, and FAULTMASK handlers.

When the MPU is enabled:

相关PDF资料 |

PDF描述 |

|---|---|

| MPC565CZP56 | IC MPU 32BIT IM FLASH 388-PBGA |

| C8051F587-IQ | IC 8051 MCU 96K FLASH 32-QFP |

| MC68HC11F1CFN2 | IC MCU 512 EEPROM 2MHZ 68-PLCC |

| MC68HC11F1CFN3 | IC MCU 512 EEPROM 3MHZ 68-PLCC |

| MC68HC11F1CFN4 | IC MCU 512 EEPROM 4MHZ 68-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EFM32TG210F32-QFN32 | 制造商:Energy Micro AS 功能描述:TINY GECKO MCU - Tape and Reel 制造商:Energy Micro AS 功能描述:TINY GECKO MCU - Cut TR (SOS) 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 32KB FLASH 32QFN |

| EFM32TG210F32-QFN32T | 制造商:Energy Micro AS 功能描述:32 BIT ARM MPU, TINY GECKO - Trays |

| EFM32TG210F32-QFN32-T | 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 32KB FLASH 32QFN |

| EFM32-TG210F32-SK | 功能描述:IC MICRO KIT GECKO 32QFN RoHS:是 类别:套件 >> 半导体产品 - IC 元件分类 系列:Tiny Gecko 其它有关文件:NXPLOGIC2-KIT-ND Contents 标准包装:1 系列:74AUP 套件类型:逻辑 值:180 件 - 18 种值各 10 件 包装:- 安装类型:表面贴装 包括封装:6-XSON,8-XSON,8-XQFN 产品目录页面:2653 (CN2011-ZH PDF) 工具箱内容:(10) 568-4391-1-ND - IC GATE MULT-FUNC CONFIG 6-XSON(10) 568-4390-1-ND - IC CONFIG MULT-FUNC GATE 6-XSON(10) 568-4389-1-ND - IC GATE DUAL FUNCTION 8-XSON(10) 568-4388-1-ND - IC GATE DUAL FUNCTION 8-XQFN(10) 568-4387-1-ND - IC F-F D-TYPE POS EDGE 8-XSON(10) 568-4386-1-ND - IC F-F D-TYPE POS EDGE 8-XQFN(10) 568-4385-1-ND - IC CONFIG MULTI-FUNC GATE 6-XSON(10) 568-4384-1-ND - IC EX-OR GATE 3-IN 6-XSON(10) 568-4383-1-ND - IC F-F D-TYPE POS EDGE 6-XSON(10) 568-4382-1-ND - IC LATCH D-TYPE 6-XSON更多... 其它名称:NXPLOGIC2-KIT |

| EFM32TG210F32-T | 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 32KB FLASH 32QFN |

发布紧急采购,3分钟左右您将得到回复。