参数资料

| 型号: | EP4S100G5F45I1 |

| 厂商: | Altera |

| 文件页数: | 16/22页 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 530K 1932FBGA |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 3 |

| 系列: | STRATIX® IV GT |

| LAB/CLB数: | 21248 |

| 逻辑元件/单元数: | 531200 |

| RAM 位总计: | 28033024 |

| 输入/输出数: | 781 |

| 电源电压: | 0.92 V ~ 0.98 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 1932-BBGA |

| 供应商设备封装: | 1932-FBGA(45x45) |

Chapter 1: Overview for the Stratix IV Device Family

1–3

Feature Summary

September 2012

Altera Corporation

Stratix IV GX Devices

Stratix IV GX devices provide up to 48 full-duplex CDR-based transceiver channels

per device:

■

Thirty-two out of the 48 transceiver channels have dedicated physical coding

sublayer (PCS) and physical medium attachment (PMA) circuitry and support

data rates between 600 Mbps and 8.5 Gbps

■

The remaining 16 transceiver channels have dedicated PMA-only circuitry and

support data rates between 600 Mbps and 6.5 Gbps

1 The actual number of transceiver channels per device varies with device selection. For

more information about the exact transceiver count in each device, refer to Table 1–1

1 For more information about transceiver architecture, refer to the Transceiver

Architecture in Stratix IV Devices chapter.

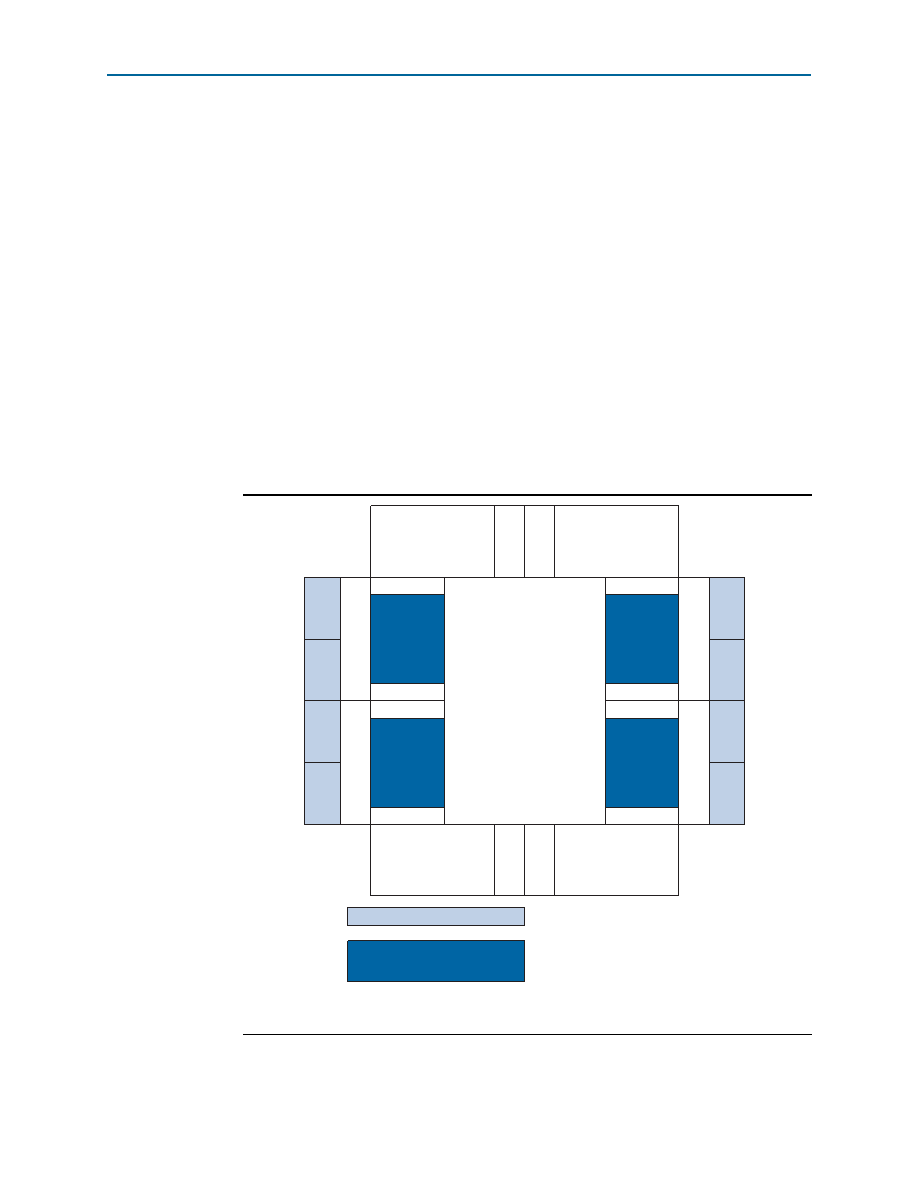

Figure 1–1 shows a high-level Stratix IV GX chip view.

Figure 1–1. Stratix IV GX Chip View (1)

Note to Figure 1–1:

(1) Resource counts vary with device selection, package selection, or both.

General Purpose

I/O and Memory

Interface

600 Mbps-8.5 Gbps CDR-based Transceiver

General Purpose I/O and 150 Mbps-1.6 Gbps

LVDS interface with DPA and Soft-CDR

T

ransceiv

er

Bloc

k

T

ransceiv

er

Bloc

k

T

ransceiv

er

Bloc

k

T

ransceiv

er

Bloc

k

PCI

Express

Hard

IP

Bloc

k

PCI

Express

Hard

IP

Bloc

k

PCI

Express

Hard

IP

Bloc

k

PCI

Express

Hard

IP

Bloc

k

General Purpose

I/O and Memory

Interface

PLL

General Purpose

I/O and Memory

Interface

General Purpose

I/O and Memory

Interface

PLL

FPGA Fabric

(Logic Elements, DSP,

Embedded Memory,

Clock Networks)

Transceiver Block

General Purpose I/O and

High-Speed LVDS I/O

with DPA and Soft CDR

Gener

al

Pur

pose

I/O

and

High-Speed

LVDS

I/O

with

DP

A

and

Soft

CDR

PLL

T

ransceiv

er

Bloc

k

T

ransceiv

er

Bloc

k

T

ransceiv

er

Bloc

k

T

ransceiv

er

Bloc

k

Gener

al

Pur

pose

I/O

and

High-Speed

LVDS

I/O

with

DP

A

and

Soft

CDR

Gener

al

Pur

pose

I/O

and

High-Speed

LVDS

I/O

with

DP

A

and

Soft

CDR

Gener

al

Pur

pose

I/O

and

High-Speed

LVDS

I/O

with

DP

A

and

Soft

CDR

相关PDF资料 |

PDF描述 |

|---|---|

| EP4SGX530NF45C3NES | IC STRATIX IV GX 530K 1932-FBGA |

| EP7309-CV | IC ARM720T MCU 74MHZ 208-LQFP |

| EP7311-IV-90 | IC ARM720T MCU 90MHZ 208-LQFP |

| EP7312-IV-90 | IC ARM720T MCU 90MHZ 208-LQFP |

| EP9301-CQZ | IC ARM9 SOC PROCESSOR 208LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP4S100G5F45I1N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4S100G5F45I1NGA | 制造商:Altera Corporation 功能描述: |

| EP4S100G5F45I2 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4S100G5F45I2N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4S100G5F45I3 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV 21248 LABs 781 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。