- 您现在的位置:买卖IC网 > PDF目录16569 > EVAL-AD2S1200SDZ (Analog Devices Inc)BOARD EVAL FOR AD2S1200 PDF资料下载

参数资料

| 型号: | EVAL-AD2S1200SDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD2S1200 |

| 标准包装: | 1 |

| 主要目的: | 接口,旋转变压至数字 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD2S1200 |

| 主要属性: | 图形用户界面(GUI) |

| 已供物品: | 板,CD,电源 |

AD2S1200

Rev. 0 | Page 17 of 24

Synthetic Reference Generation

When a resolver undergoes a high rotation rate, the RDC tends

to act as an electric motor and produces speed voltages, along

with the ideal Sin and Cos outputs. These speed voltages are in

quadrature to the main signal waveform. Moreover, nonzero

resistance in the resolver windings causes a non-zero phase shift

between the reference input and the Sin and Cos outputs. The

combination of speed voltages and phase shift causes a tracking

error in the RDC that is approximated by

Frequency

Reference

Rate

Rotation

Shift

Phase

Error

×

=

To compensate for the described phase error between the

resolver reference excitation and the Sin/Cos signals, an internal

synthetic reference signal is generated in phase with the refer-

ence frequency carrier. The synthetic reference is derived using

the internally filtered Sin and Cos signals. It is generated by

determining the zero crossing of either the Sin or Cos (which-

ever signal is larger, to improve phase accuracy) and evaluating

the phase of the resolver reference excitation. The synthetic

reference reduces the phase shift between the reference and

Sin/Cos inputs to less than 10°, and will operate for phase shifts

of ±45°.

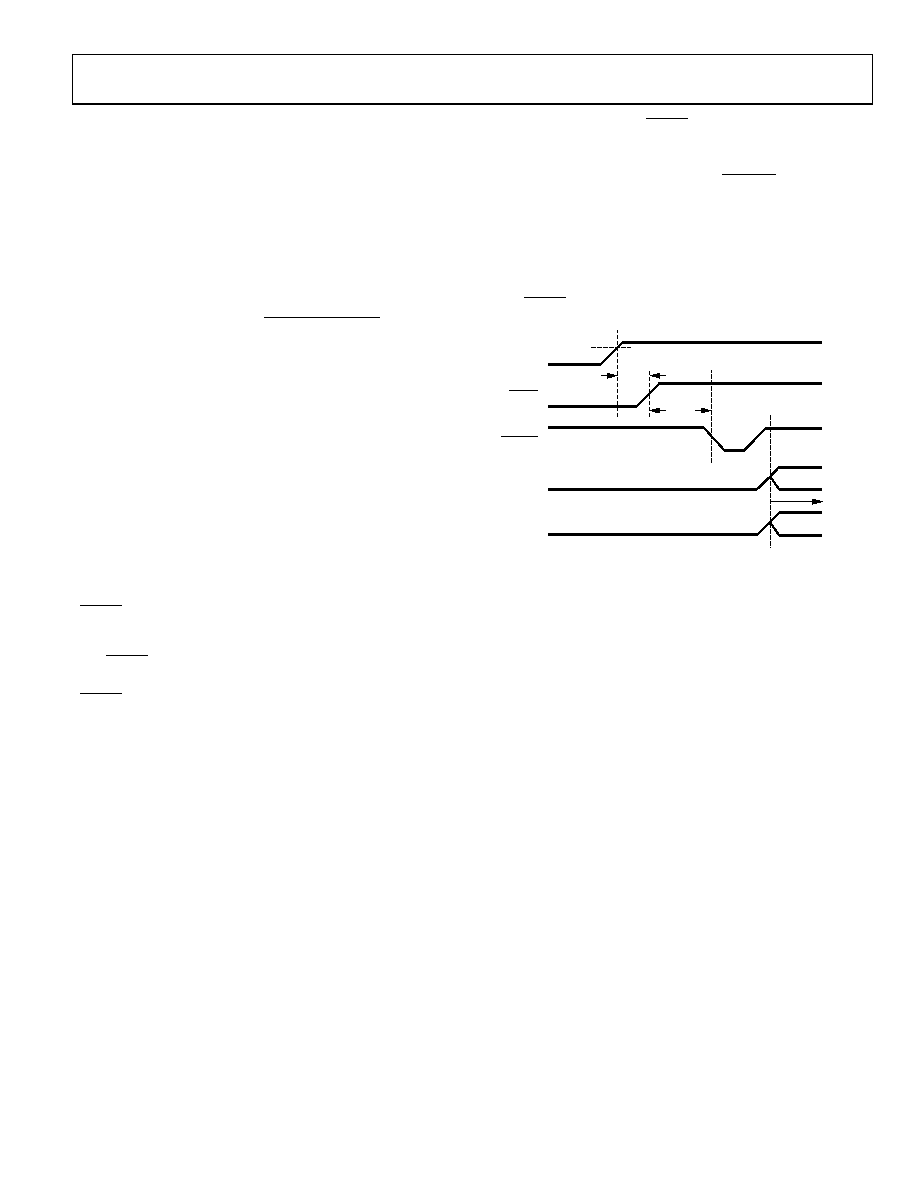

SUPPLY SEQUENCING AND RESET

The AD2S1200 requires an external reset signal to hold the

RESET input low until VDD is within the specified operating

range of 4.5 V to 5.5 V.

The RESET pin must be held low for a minimum of 10 s after

RESET signal to the AD2S1200 initializes the output position to

a value of 0x000 (degrees output through the parallel, serial, and

encoder interfaces) and causes LOS to be indicated (LOT and

DOS pins pulled low) as shown in Figure 10.

Failure to apply the above (correct) power-up/reset sequence

can result in an incorrect position indication.

After a rising edge on the RESET input, the device must be

circuitry to stabilize and the tracking loop to settle to the step

change in input position. After tTRACK, a SAMPLE pulse must be

applied, releasing the LOT and DOT pins to the state deter-

mined by the fault detection circuitry and providing valid

position data at the parallel and serial outputs (note that if

position data is being acquired via the encoder outputs, they

may be monitored during tTRACK).

The RESET pin is internally pulled up.

tRST

04406-0-010

VDD

RESET

4.75V

VALID

OUTPUT

DATA

SAMPLE

LOT

DOS

tTRACK

Figure 10. Power Supply Sequencing and Reset

CHARGE PUMP OUTPUT

A 204.8 kHz square wave output with 50% duty cycle is avail-

able at the CPO output pin of the AD2S1200. This square wave

output can be used for negative rail voltage generation, or to

create a VCC rail.

相关PDF资料 |

PDF描述 |

|---|---|

| GEC10DRAI-S734 | CONN EDGECARD 20POS .100 R/A SLD |

| EBM25DCAI-S189 | CONN EDGECARD 50POS R/A .156 SLD |

| H6MMS-5018M | DIP CABLE - HDM50S/AE50M/HDM50S |

| A3CCH-1618M | IDC CABLE - AKC16H/AE16M/AKC16H |

| GBC10DRAH-S734 | CONN EDGECARD 20POS .100 R/A SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD2S1205CBZ | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. |

| EVAL-AD2S1205SDZ | 功能描述:BOARD EVAL FOR AD2S1205 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD2S1210EDZ | 功能描述:BOARD EVAL AD2S1210 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| EVAL-AD4001FMCZ | 功能描述:EVAL BOARD FOR AD4001 制造商:analog devices inc. 系列:- 零件状态:在售 A/D 转换器数:1 位数:16 采样率(每秒):2M 数据接口:SPI,DSP 输入范围:±VREF 不同条件下的功率(典型值):20mW @ 2MSPS 使用的 IC/零件:AD4001 所含物品:板,电源 标准包装:1 |

| EVAL-AD421EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Loop-Powered 4 mA to 20 mA DAC |

发布紧急采购,3分钟左右您将得到回复。