- 您现在的位置:买卖IC网 > PDF目录16427 > EVAL-ADAU1442EBZ (Analog Devices Inc)BOARD EVAL FOR ADAU1442 PDF资料下载

参数资料

| 型号: | EVAL-ADAU1442EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 26/93页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADAU1442 |

| 标准包装: | 1 |

| 系列: | SigmaDSP® |

| 主要目的: | 音频,音频处理 |

| 嵌入式: | 是,DSP |

| 已用 IC / 零件: | ADAU1442 |

| 主要属性: | 单芯片多通道 28/56 位音频 DSP |

| 次要属性: | I²C & SPI 接口 |

| 已供物品: | 电路板,线缆,说明文档,GPIO 子板,电源 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

Data Sheet

ADAU1442/ADAU1445/ADAU1446

Rev. D | Page 31 of 92

SERIAL DATA INPUT/OUTPUT

The flexible serial data input and output ports of the ADAU1442/

a 2-channel (usually I2S format), packed TDM4, or standard 4-, 8-,

or 16-channel TDM stream. Data is processed in twos complement,

MSB-first format. The left-channel data field always precedes the

right-channel data field in 2-channel streams. In the TDMn modes

(where n represents the total number of channels in the stream),

Slot 0 to Slot (n/2) 1 fall in the first half of the audio frame, and

Slot n/2 to Slot n 1 are in the second half of the frame. TDM

mode allows fewer serial data pins to be used, freeing more pins

for other data streams. The serial modes are set in the serial output

port modes and serial input port modes control registers.

When referring to audio data streams, the terms TDM2 and I2S

should be treated with care. In this document, TDM2 refers to

any 2-channel stream, whereas I2

S refers specifically to a 2-channel,

negative BCLK polarity, negative LRCLK polarity, MSB delay-

by-1 stream.

The serial data clocks are fully bidirectional and do not need to

master clock input. However, asynchronous data streams must

be routed through an on-board asynchronous sample rate

converter to be processed in the core.

The input control registers allow control of clock polarity and data

input modes. All common data formats are available with flexible

MSB start, bit depth (24-, 20-, or 16-bit), and TDM settings. In all

modes except the right-justified modes, the serial port accepts an

arbitrary number of bits up to a limit of 24. Extra bits do not

cause an error, but they are truncated internally. Proper operation

of the right-justified modes requires that there be exactly 64 BCLKs

per audio frame (for 2-channel data). The LRCLK in TDM mode

a 50/50 duty cycle clock or as a bit-wide pulse.

In TDM mode, the bit clock supplied by the ADAU1442/

This, in turn, limits the sampling rate at which it can supply

master clocks in various TDM modes. Table 18 displays the

modes in which the serial output port functions for some

common audio sample rates.

The output control registers give the user control of clock polarities,

clock frequencies, clock types, and data format. In all modes except

the right-justified modes (MSB delayed by 8, 12, or 16), the serial

port accepts an arbitrary number of bits up to a limit of 24.

Extra bits do not cause an error, but are truncated internally.

Proper operation of the right-justified modes requires the LSB

to align with the edge of the LRCLK. The default settings of all

serial port control registers correspond to 2-channel, I2S mode,

and 24-bit slave mode, and these registers are set as slaves to the

clock domain corresponding to their channel number.

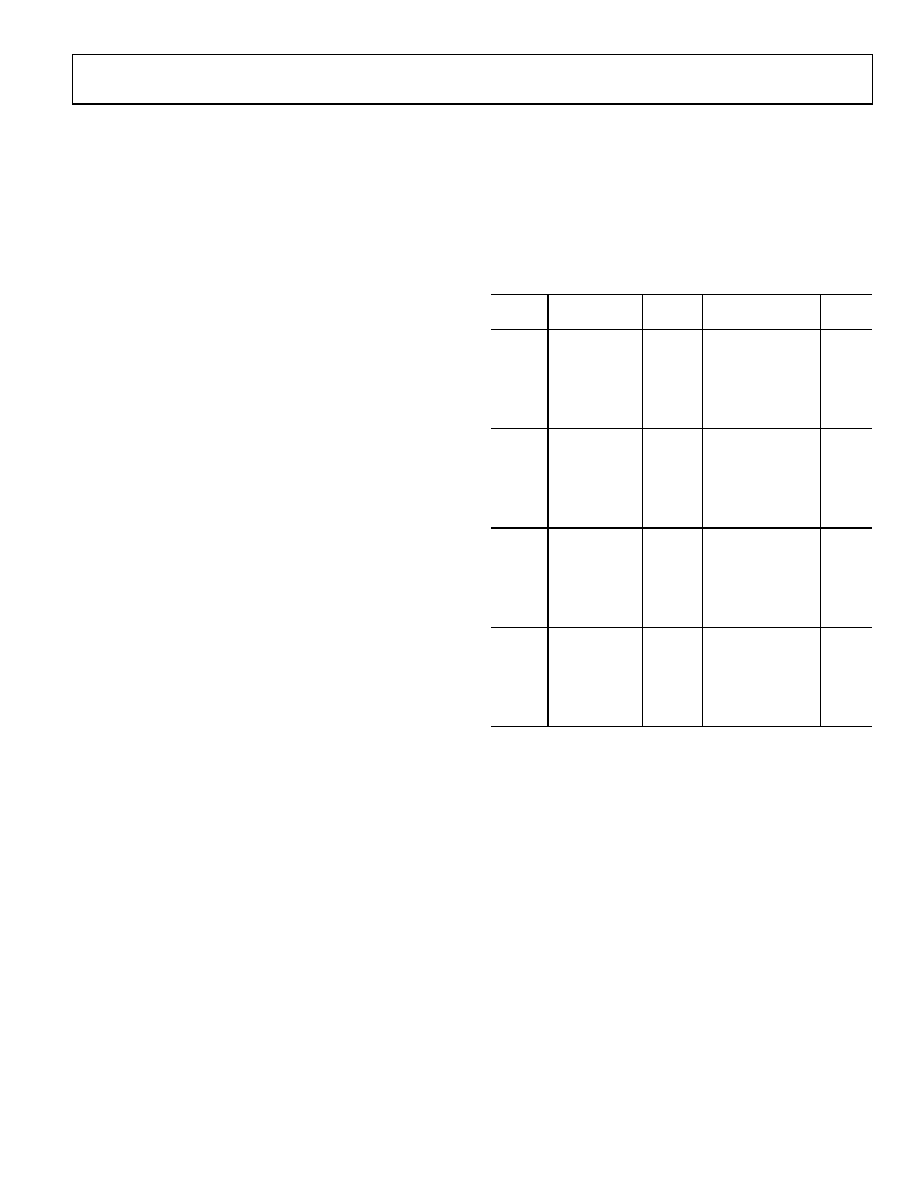

Table 18. Serial Input and Output Port TDM Capabilities

Mode

BCLK Cycles

per Frame

fS (kHz)

BCLK

Frequency (MHz)

Valid

Mode

TDM2

64

44.1

2.8224

Yes

64

48

3.072

Yes

64

88.2

5.6448

Yes

64

96

6.144

Yes

64

192

12.288

Yes

TDM4

128

44.1

5.6448

Yes

128

48

6.144

Yes

128

88.2

11.2896

Yes

128

96

12.288

Yes

128

192

24.576

Yes

TDM8

256

44.1

11.2896

Yes

256

48

12.288

Yes

256

88.2

22.5792

Yes

256

96

24.576

Yes

256

192

49.152

TDM16

512

44.1

22.5792

Yes

512

48

24.576

Yes

512

88.2

45.1584

512

96

49.152

512

192

98.304

1

The device will not work in this mode.

Connections to an external DAC are handled exclusively with

the output port pins. The output LRCLKx and BCLKx pins can

be set to be either master or slave, and the SDATA_OUT pins

are used to output data from the SigmaDSP to the external DAC.

Table 19 shows the proper configurations for standard audio

data formats, and Figure 21 presents an overview of the serial

data input/output ports.

相关PDF资料 |

PDF描述 |

|---|---|

| A3AAH-4036G | IDC CABLE - ASC40H/AE40G/ASC40H |

| AMIS30622C6227RG | IC MOTOR DVR MICROSTP I2C 20SOIC |

| A1CXB-3036M | IDC CABLE- AKC30B/AE30M/X |

| VE-214-EX | CONVERTER MOD DC/DC 48V 75W |

| GCC10DRYH-S734 | CONN EDGECARD 20POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADAU1446EBZ | 功能描述:BOARD EVAL FOR ADAU1446 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADAU1590EBZ | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

| EVAL-ADAU1592EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For ADAU1592 制造商:Analog Devices 功能描述:EVAL BOARD - Boxed Product (Development Kits) |

| EVAL-ADAU1701EB | 制造商:Analog Devices 功能描述:EVAL BOARD FOR SIGMADSP AUDIO PROCESSOR - Bulk |

| EVAL-ADAU1701EBZ | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

发布紧急采购,3分钟左右您将得到回复。